# In the Matter of

# CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

Investigation No. 337-TA-1044

**Publication 4964**

September 2019

# U.S. International Trade Commission

Washington, DC 20436

# U.S. International Trade Commission

# **COMMISSIONERS**

David Johanson, Chairman Irving Williamson, Commissioner Meredith Broadbent, Commissioner Rhonda Schmidtlein, Commissioner

Address all communications to Secretary to the Commission United States International Trade Commission Washington, DC 20436

# **U.S. International Trade Commission**

Washington, DC 20436 www.usitc.gov

# In the Matter of

# CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

Investigation No. 337-TA-1044

#### UNITED STATES INTERNATIONAL TRADE COMMISSION

Washington, D.C.

In the Matter of

CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME Investigation No. 337-TA-1044

NOTICE OF COMMISSION FINAL DETERMINATION FINDING A SECTION 337 VIOLATION; ISSUANCE OF A LIMITED EXCLUSION ORDER AND CEASE AND DESIST ORDERS; DENIAL OF MOTION TO AMEND; AND TERMINATION OF THE INVESTIGATION

**AGENCY**: U.S. International Trade Commission.

**ACTION**: Notice.

SUMMARY: Notice is hereby given that the U.S. International Trade Commission has found a violation of section 337 of the Tariff Act of 1930 ("section 337"), as amended, in this investigation. The Commission has issued a limited exclusion order prohibiting the importation of certain graphics systems and televisions containing the same that infringe claim 1-5 and 8 of U.S. Patent No. 7,633,506 ("the '506 patent"). The Commission has also issued cease and desist orders directed to Respondents VIZIO, Inc. ("VIZIO") and Sigma Designs, Inc. ("SDI"). The Commission has further determined to deny Complainants' motion for leave to amend the complaint and the notice of investigation. The investigation is terminated.

FOR FURTHER INFORMATION CONTACT: Houda Morad, Office of the General Counsel, U.S. International Trade Commission, 500 E Street SW., Washington, DC 20436, telephone (202) 708-4716. Copies of non-confidential documents filed in connection with this investigation are or will be available for inspection during official business hours (8:45 a.m. to 5:15 p.m.) in the Office of the Secretary, U.S. International Trade Commission, 500 E Street SW., Washington, D.C. 20436, telephone (202) 205-2000. General information concerning the Commission may also be obtained by accessing its Internet server at <a href="https://www.usitc.gov">https://www.usitc.gov</a>. The public record for this investigation may be viewed on the Commission's electronic docket (EDIS) at <a href="https://edis.usitc.gov">https://edis.usitc.gov</a>. Hearing-impaired persons are advised that information on this matter can be obtained by contacting the Commission's TDD terminal on (202) 205-1810.

**SUPPLEMENTARY INFORMATION**: The Commission instituted Investigation No. 337-TA-1044 on March 22, 2017, based on a complaint filed by Complainants Advanced Micro Devices, Inc. of Sunnyvale, California and ATI Technologies ULC of Canada (collectively,

"AMD" or "Complainants"). See 82 FR 14748 (Mar. 22, 2017). The complaint, as amended, alleges violations of section 337 of the Tariff Act of 1930, as amended (19 U.S.C. 1337), based upon the importation into the United States, the sale for importation, and the sale within the United States after importation of certain graphics systems, components thereof, and consumer products containing the same, by reason of infringement of certain claims of the '506 patent; U.S. Patent No. 7,796,133 ("the '133 patent"); U.S. Patent No. 8,760,454 ("the '454 patent"); and U.S. Patent No. 9,582,846 ("the '846 patent"). Id. The notice of investigation identified LG Electronics, Inc. of Seoul, Republic of Korea, LG Electronics U.S.A., Inc. of Englewood Cliffs, New Jersey, and LG Electronics MobileComm U.S.A. Inc. of San Diego, California (collectively, "LG"), VIZIO of Irvine, California, MediaTek Inc. of Hsinchu City, Taiwan and Media Tek USA Inc. of San Jose, California (collectively, "MediaTek"), and SDI of Fremont, California, as respondents in this investigation. See id. The Office of Unfair Import Investigations ("OUII") is also a party to the investigation.

On October 20, 2017, the ALJ issued an initial determination terminating the investigation as to LG based on settlement. *See* Order No. 48 (Oct. 20, 2017), *unreviewed*, Comm'n Notice (Nov. 13, 2017). The remaining respondents in this investigation are VIZIO, MediaTek, and SDI (hereinafter, "the Remaining Respondents"). The ALJ also terminated the investigation with respect to all asserted claims of the '454 and '846 patents; claims 6, 7, and 9 of the '506 patent; and claims 2, 4-13, and 40 of the '133 patent. *See* Order No. 33 (Aug. 15, 2017), *unreviewed*, Comm'n Notice (Sept. 5, 2017); Order No. 43 (Oct. 5, 2017), *unreviewed*, Comm'n Notice (Nov. 13, 2017); Order No. 53 (Oct. 31, 2017), *unreviewed*, Comm'n Notice (Nov. 28, 2017). Claims 1-5 and 8 of the '506 patent and claims 1 and 3 of the '133 patent (hereinafter, "the asserted claims") remain pending in this investigation.

On April 13, 2018, the ALJ issued her final Initial Determination ("FID") and Recommended Determination on Remedy and Bond ("RD") finding a violation of section 337 with respect to the '506 patent but not the '133 patent. Specifically, the FID finds that: (1) certain accused products infringe the asserted claims of the '506 patent but not the '133 patent; (2) the asserted claims are not invalid; and (3) Complainants satisfy the economic and technical prongs of the domestic industry requirement with respect to both asserted patents. In addition, the ALJ recommended that the Commission issue: (1) a Limited Exclusion Order against the infringing accused products; and (2) Cease and Desist Orders against Respondents VIZIO and SDI. The ALJ further recommended against setting a bond during Presidential review.

On June 14, 2018, the Commission issued a Notice determining to review the FID in part. See 83 FR 28660-62 (June 20, 2018). The Commission sought written submissions in response to certain questions relating to the claim construction of the terms "unified shader" (recited in the '506 and '133 patent claims), "packet" (recited in the '133 patent claims), and "ALU/memory pair" (recited in the '133 patent claims). See id. The Commission also solicited written submissions on the issues of remedy, the public interest, and bonding. See id. On June 28, 2018, the parties filed written submissions in response to the June 14, 2018 Notice, and on July 6, 2018, the parties filed responses to each other's submissions.

On June 26, 2018, Complainants filed a motion for leave to amend the complaint and notice of investigation to add V-Silicon Inc. and V-Silicon International, Inc. as respondents in this investigation (*Motion*). On July 5 and 6, 2018, OUII and Respondents, respectively, filed responses to Complainants' motion to amend. As explained in the Commission's Opinion issued concurrently herewith, the Commission has determined to deny Complainants' *Motion*.

In addition, having examined the record of this investigation, including the FID, the RD, and the parties' submissions, the Commission has determined to affirm the FID's ultimate conclusions of a section 337 violation with respect to the '506 patent and no section 337 violation with respect to the '133 patent. In addition, the Commission has determined to modify the FID in part with respect to: (1) the importation requirement as to Respondents MediaTek and SDI; and (2) the claim construction of the terms "unified shader," "packet," and "ALU/memory pair" as well as certain related FID findings on infringement, validity, and the technical prong of the domestic industry requirement. All findings in the FID that are not inconsistent with the Commission's determination are affirmed.

Accordingly, the Commission finds that there is a violation of section 337 with respect to the '506 patent. The Commission has determined that the appropriate remedy is a limited exclusion order against Respondents' infringing products, and cease and desist orders against Respondents VIZIO and SDI. The Commission has also determined that the public interest factors enumerated in subsections 337(d)(l) and (f)(1) (19 U.S.C. 1337(d)(l), (f)(1)) do not preclude the issuance of the limited exclusion order and cease and desist orders. The Commission has further determined to set a bond at zero (0) percent of entered value during the Presidential review period (19 U.S.C. 1337(j)).

The Commission's orders and opinion were delivered to the President and to the United States Trade Representative on the day of their issuance.

The authority for the Commission's determination is contained in section 337 of the Tariff Act of 1930, as amended (19 U.S.C. 1337), and in part 210 of the Commission's Rules of Practice and Procedure (19 CFR part 210).

By order of the Commission.

Lisa R. Barton

Secretary to the Commission

Issued: August 22, 2018

# CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

# **PUBLIC CERTIFICATE OF SERVICE**

I, Lisa R. Barton, hereby certify that the attached **NOTICE** has been served by hand upon the Commission Investigative Attorney, Yoncha L. Kundupoglu, Esq., and the following parties as indicated, on 8/22/2018

Lisa R. Barton, Secretary U.S. International Trade Commission 500 E Street, SW, Room 112 Washington, DC 20436

| On Behalf of Complainants:                                                                                                                         |                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Michael T. Renaud, Esq.  MINTZ LEVIN COHN FERRIS GLOVSKY AND POPEO PC  One Financial Center  Boston, MA 02111                                      | <ul><li>□ Via Hand Delivery</li><li>⋈ Via Express Delivery</li><li>□ Via First Class Mail</li><li>□ Other:</li></ul> |

| On Behalf of Respondents VIZIO, Inc.:                                                                                                              |                                                                                                                      |

| Cono A. Carrano, Esq. <b>AKIN GUMP STRAUSS HAUER &amp; FELD LLP</b> Robert S. Strauss Building  1333New Hampshire Avenue, NW  Washington, DC 20036 | <ul><li>□ Via Hand Delivery</li><li>⋈ Via Express Delivery</li><li>□ Via First Class Mail</li><li>□ Other:</li></ul> |

| On Behalf of Respondents MediaTek, Inc., MediaTek USA Inc., and Sigma Designs, Inc.:                                                               |                                                                                                                      |

| Tyler T. VanHoutan, Esq.  MCGUIREWOODS LLP  600 Travis Street, Suite 7500  Houston, TX 77002                                                       | <ul><li>□ Via Hand Delivery</li><li>☑ Via Express Delivery</li><li>□ Via First Class Mail</li><li>□ Other:</li></ul> |

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

Investigation No. 337-TA-1044

# MODIFIED LIMITED EXCLUSION ORDER

The United States International Trade Commission ("Commission") has determined that there is a violation of Section 337 of the Tariff Act of 1930, as amended (19 U.S.C. § 1337), in the unlawful importation, sale for importation, or sale within the United States after importation by Respondents MediaTek Inc. and Media Tek USA Inc. (collectively, "MediaTek"), and Sigma Designs, Inc. ("SDI") (collectively, "Respondents"), of certain graphics systems, components thereof, and consumer products containing the same, covered by claims 1-5 and 8 of U.S. Patent No. 7,633,506 ("the '506 patent").

Having reviewed the record of this investigation, including the written submissions of the parties, the Commission has made its determination on the issues of remedy, public interest, and bonding. The Commission has determined that the appropriate form of relief is a limited exclusion order prohibiting the unlicensed entry into the United States of MediaTek's and SDI's covered graphics systems, manufactured abroad by or on behalf of the Respondents or any of their affiliated companies, parents, subsidiaries, or other related business entities, or their successors or assigns.

The Commission has also determined that the public interest factors enumerated in 19 U.S.C. § 1337(d) do not preclude the issuance of the limited exclusion order, and that the bond

during the Presidential review period shall be in the amount of zero (0) percent of the entered value of the covered products.

Accordingly, the Commission hereby **ORDERS** that:

- 1. MediaTek's and SDI's graphics systems covered by one or more of claims 1-5 and 8 of the '506 patent that are manufactured abroad by or on behalf of, or are imported by or on behalf of the Respondents or any of their affiliated companies, parents, subsidiaries, agents, or other related business entities, or their successors or assigns are excluded from entry for consumption into the United States, entry for consumption from a foreign-trade zone, or withdrawal from a warehouse for consumption, for the remaining term of the '506 patent, except under license of the patent owner or as provided by law.

- 2. Notwithstanding paragraph 1 of this Order, the aforesaid graphics systems, components thereof, and consumer products containing the same, are entitled to entry into the United States for consumption, entry for consumption from a foreign trade zone, or withdrawal from a warehouse for consumption, under bond in the amount of zero (0) percent of the entered value of the covered products pursuant to subsection (j) of section 337 of the Tariff Act of 1930, as amended (19 U.S.C. § 1337(j)), and the Presidential Memorandum for the United States Trade Representative of July 21, 2005, (70 FR 43251), from the day after this Order is received by the United States Trade Representative, and until such time as the United States Trade representative notifies the Commission that this Order is approved or disapproved but, in any event, not later than sixty (60) days after the date of receipt of this Order.

- 3. At the discretion of U.S. Customs and Border Protection ("CBP") and pursuant to the procedures it establishes, persons seeking to import graphics systems, components thereof, and consumer products containing the same, that are potentially subject to this Order may be

required to certify that they are familiar with the terms of this Order, that they have made

appropriate inquiry, and thereupon state that, to the best of their knowledge and belief, the

products being imported are not excluded from entry under paragraph 1 of this Order. At its

discretion, CBP may require persons who have provided the certification described in this

paragraph to furnish such records or analyses as are necessary to substantiate this certification.

4. In accordance with 19 U.S.C. § 1337(l), the provisions of this Order shall not

apply to graphics systems, components thereof, and consumer products containing the same that

are imported by or for the use of the United States, or imported for and to be used for, the United

States with the authorization or consent of the Government.

5. The Commission may modify this Order in accordance with the procedures

described in Rule 210.76 of the Commission's Rules of Practice and Procedure (19 C.F.R. §

210.76).

The Secretary shall serve copies of this Order upon each party of record in this 6.

Investigation and upon CBP.

Notice of this Order shall be published in the Federal Register. 7.

By order of the Commission.

Lisa R. Barton

Secretary to the Commission

Issued: October 5, 2018

3

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

Investigation No. 337-TA-1044

# MODIFIED LIMITED EXCLUSION ORDER

The United States International Trade Commission ("Commission") has determined that there is a violation of Section 337 of the Tariff Act of 1930, as amended (19 U.S.C. § 1337), in the unlawful importation, sale for importation, or sale within the United States after importation by Respondents MediaTek Inc. and Media Tek USA Inc. (collectively, "MediaTek"), and Sigma Designs, Inc. ("SDI") (collectively, "Respondents"), of certain graphics systems, components thereof, and consumer products containing the same, covered by claims 1-5 and 8 of U.S. Patent No. 7,633,506 ("the '506 patent").

Having reviewed the record of this investigation, including the written submissions of the parties, the Commission has made its determination on the issues of remedy, public interest, and bonding. The Commission has determined that the appropriate form of relief is a limited exclusion order prohibiting the unlicensed entry into the United States of MediaTek's and SDI's covered graphics systems, manufactured abroad by or on behalf of the Respondents or any of their affiliated companies, parents, subsidiaries, or other related business entities, or their successors or assigns.

The Commission has also determined that the public interest factors enumerated in 19 U.S.C. § 1337(d) do not preclude the issuance of the limited exclusion order, and that the bond

during the Presidential review period shall be in the amount of zero (0) percent of the entered value of the covered products.

Accordingly, the Commission hereby **ORDERS** that:

- 1. MediaTek's and SDI's graphics systems covered by one or more of claims 1-5 and 8 of the '506 patent that are manufactured abroad by or on behalf of, or are imported by or on behalf of the Respondents or any of their affiliated companies, parents, subsidiaries, agents, or other related business entities, or their successors or assigns are excluded from entry for consumption into the United States, entry for consumption from a foreign-trade zone, or withdrawal from a warehouse for consumption, for the remaining term of the '506 patent, except under license of the patent owner or as provided by law.

- 2. Notwithstanding paragraph 1 of this Order, the aforesaid graphics systems, components thereof, and consumer products containing the same, are entitled to entry into the United States for consumption, entry for consumption from a foreign trade zone, or withdrawal from a warehouse for consumption, under bond in the amount of zero (0) percent of the entered value of the covered products pursuant to subsection (j) of section 337 of the Tariff Act of 1930, as amended (19 U.S.C. § 1337(j)), and the Presidential Memorandum for the United States Trade Representative of July 21, 2005, (70 FR 43251), from the day after this Order is received by the United States Trade Representative, and until such time as the United States Trade representative notifies the Commission that this Order is approved or disapproved but, in any event, not later than sixty (60) days after the date of receipt of this Order.

- 3. At the discretion of U.S. Customs and Border Protection ("CBP") and pursuant to the procedures it establishes, persons seeking to import graphics systems, components thereof, and consumer products containing the same, that are potentially subject to this Order may be

required to certify that they are familiar with the terms of this Order, that they have made

appropriate inquiry, and thereupon state that, to the best of their knowledge and belief, the

products being imported are not excluded from entry under paragraph 1 of this Order. At its

discretion, CBP may require persons who have provided the certification described in this

paragraph to furnish such records or analyses as are necessary to substantiate this certification.

In accordance with 19 U.S.C. § 1337(1), the provisions of this Order shall not 4.

apply to graphics systems, components thereof, and consumer products containing the same that

are imported by or for the use of the United States, or imported for and to be used for, the United

States with the authorization or consent of the Government.

5. The Commission may modify this Order in accordance with the procedures

described in Rule 210.76 of the Commission's Rules of Practice and Procedure (19 C.F.R. §

210.76).

6. The Secretary shall serve copies of this Order upon each party of record in this

Investigation and upon CBP.

7. Notice of this Order shall be published in the Federal Register.

By order of the Commission.

Lisa R. Barton

Secretary to the Commission

Issued: October 5, 2018

3

# CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

Inv. No. 337-TA-1044 (Modification Proceeding)

# PUBLIC CERTIFICATE OF SERVICE

I, Lisa R. Barton, hereby certify that the attached **ORDER, COMMISSION** has been served by hand upon the Commission Investigative Attorney, Yoncha L. Kundupoglu, Esq., and the following parties as indicated, on 10/5/2018

Lisa R. Barton, Secretary U.S. International Trade Commission 500 E Street, SW, Room 112 Washington, DC 20436

| On Behalf of Complainants:                                                                                                                |                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Michael T. Renaud, Esq.  MINTZ LEVIN COHN FERRIS GLOVSKY AND POPEO PC  One Financial Center  Boston, MA 02111                             | <ul><li>□ Via Hand Delivery</li><li>⋈ Via Express Delivery</li><li>□ Via First Class Mail</li><li>□ Other:</li></ul> |

| On Behalf of Respondents VIZIO, Inc.:                                                                                                     |                                                                                                                      |

| Cono A. Carrano, Esq.  AKIN GUMP STRAUSS HAUER & FELD LLP  Robert S. Strauss Building  1333New Hampshire Avenue, NW  Washington, DC 20036 | <ul><li>□ Via Hand Delivery</li><li>⋈ Via Express Delivery</li><li>□ Via First Class Mail</li><li>□ Other:</li></ul> |

| On Behalf of Respondents MediaTek, Inc. and MediaTek USA                                                                                  |                                                                                                                      |

| Inc.                                                                                                                                      |                                                                                                                      |

| Tyler T. VanHoutan, Esq.  MCGUIREWOODS LLP  600 Travis Street, Suite 7500  Houston, TX 77002                                              | <ul><li>□ Via Hand Delivery</li><li>⋈ Via Express Delivery</li><li>□ Via First Class Mail</li><li>□ Other:</li></ul> |

| Respondents:                                                                                                                              |                                                                                                                      |

| Sigma Designs, Inc. Legal Department 47467 Fremont Boulevard Fremont, CA 94538                                                            | <ul><li>□ Via Hand Delivery</li><li>⋈ Via Express Delivery</li><li>□ Via First Class Mail</li><li>□ Other:</li></ul> |

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

Investigation No. 337-TA-1044

#### CEASE AND DESIST ORDER

IT IS HEREBY ORDERED THAT RESPONDENT VIZIO, Inc. of Irvine, California ("Respondent"), cease and desist from conducting any of the following activities in the United States: importing, selling, marketing, advertising, distributing, transferring (except for exportation), and soliciting U.S. agents or distributors for, certain graphics systems, components thereof, and consumer products containing the same covered by claims 1-5 and 8 of U.S. Patent No. 7,633,506 ("the '506 patent") in violation of section 337 of the Tariff Act of 1930, as amended (19 U.S.C. § 1337).

# I. Definitions

As used in this Order:

- (A) "Commission" shall mean the United States International Trade Commission.

- (B) "Complainants" shall mean Advanced Micro Devices, Inc. of Sunnyvale, California, and ATI Technologies ULC of Ontario, Canada.

- (C) "Respondent" shall mean VIZIO, Inc. of Irvine, California.

- (D) "Person" shall mean an individual, or any non-governmental partnership, firm, association, corporation, or other legal or business entity other than Respondent or its majority owned or controlled subsidiaries, successors, or assigns.

- (E) "United States" shall mean the fifty States, the District of Columbia, and Puerto Rico.

- (F) The terms "import" and "importation" refer to importation for entry for consumption under the Customs laws of the United States.

- (G) The term "covered products" shall mean Respondent's televisions containing graphics systems covered by one or more of claims 1-5 and 8 of the '506 patent.

# II. Applicability

The provisions of this Cease and Desist Order shall apply to Respondent and to any of its principals, stockholders, officers, directors, employees, agents, distributors, controlled (whether by stock ownership or otherwise) and majority-owned business entities, successors, and assigns, and to each of them insofar as they are engaging in conduct prohibited by section III, *infra*, for, with, or otherwise on behalf of, Respondent.

# III. Conduct Prohibited

The following conduct of Respondent in the United States is prohibited by this Order.

For the remaining term of the Asserted Patent, Respondent shall not:

- (A) import or sell for importation into the United States covered products;

- (B) market, distribute, sell, or otherwise transfer (except for exportation), in the United States imported covered products;

- (C) advertise imported covered products;

- (D) solicit U.S. agents or distributors for imported covered products; or

- (E) aid or abet other entities in the importation, sale for importation, sale after importation, transfer, or distribution of covered products.

# IV. Conduct Permitted

Notwithstanding any other provision of this Order, Respondent shall be permitted:

- (A) to engage in specific conduct otherwise prohibited by the terms of this Order if, in a written instrument, the owner of the Asserted Patent licenses or authorizes such specific conduct; or

- (B) to engage in specific conduct otherwise prohibited by the terms of this Order if such specific conduct is related to the importation or sale of covered products by or for the United States.

# V. Reporting

For purposes of this requirement, the reporting periods shall commence on January 1 of each year and shall end on the subsequent December 31. The first report required under this section shall cover the period from the date of issuance of this Order through December 31, 2018. This reporting requirement shall continue in force until such time as Respondent has truthfully reported, in two consecutive timely filed reports, that it has no inventory of covered products in the United States.

Within thirty (30) days of the last day of the reporting period, Respondent shall report to the Commission: (a) the quantity in units and the value in dollars of covered products that it has (i) imported and/or (ii) sold in the United States after importation during the reporting period,

and (b) the quantity in units and value in dollars of reported covered products that remain in inventory in the United States at the end of the reporting period.

When filing written submissions, Respondent must file the original document electronically on or before the deadlines stated above and submit eight (8) true paper copies to the Office of the Secretary by noon the next day pursuant to section 210.4(f) of the Commission's Rules of Practice and Procedure (19 C.F.R. § 210.4(f)). Submissions should refer to the investigation number ("Inv. No. 337-TA-1044") in a prominent place on the cover pages and/or the first page. (See Handbook on Electronic Filing Procedures, https://www.usitc.gov/secretary/fed\_reg\_notices/rules/handbook\_on\_electronic\_filing.pdf). Persons with questions regarding filing should contact the Office of the Secretary (202-205-2000). If Respondent desires to submit a document to the Commission in confidence, it must file the original and a public version of the original with the Office of the Secretary and must serve a copy of the confidential version on Complainants' counsel.<sup>1</sup>

Any failure to make the required report or the filing of any false or inaccurate report shall constitute a violation of this Order, and the submission of a false or inaccurate report may be referred to the U.S. Department of Justice as a possible criminal violation of 18 U.S.C. § 1001.

# VI. Recordkeeping and Inspection

(A) For the purpose of securing compliance with this Order, Respondent shall retain any and all records relating to the sale, offer for sale, marketing, or distribution in the United States of covered products, made and received in the usual and ordinary course of business,

<sup>&</sup>lt;sup>1</sup> Complainants must file a letter with the Secretary identifying the attorney to receive reports associated with this Order. The designated attorney must be on the protective order entered in the investigation.

whether in detail or in summary form, for a period of three (3) years from the close of the fiscal year to which they pertain.

(B) For the purposes of determining or securing compliance with this Order and for no other purpose, subject to any privilege recognized by the federal courts of the United States, and upon reasonable written notice by the Commission or its staff, duly authorized representatives of the Commission shall be permitted access and the right to inspect and copy, in Respondent's principal office during office hours, and in the presence of counsel or other representatives if Respondent so chooses, all books, ledgers, accounts, correspondence, memoranda, and other records and documents, in detail and in summary form, that must be retained under subparagraph VI(A) of this Order.

# VII. Service of Cease and Desist Order

Respondent is ordered and directed to:

- (A) Serve, within fifteen days after the effective date of this Order, a copy of this Order upon each of its respective officers, directors, managing agents, agents, and employees who have any responsibility for the importation, marketing, distribution, or sale of imported covered products in the United States;

- (B) Serve, within fifteen days after the succession of any persons referred to in subparagraph VII(A) of this Order, a copy of this Order upon each successor; and

- (C) Maintain such records as will show the name, title, and address of each person upon whom the Order has been served, as described in subparagraphs VII(A) and VII(B) of this Order, together with the date on which service was made.

The obligations set forth in subparagraphs VII(B) and VII(C) shall remain in effect until the Asserted Patent expires.

# VIII. Confidentiality

Any request for confidential treatment of information obtained by the Commission pursuant to sections V-VI of this Order should be made in accordance with section 201.6 of the Commission's Rules of Practice and Procedure (19 C.F.R. § 201.6). For all reports for which confidential treatment is sought, Respondent must provide a public version of such report with confidential information redacted.

# IX. Enforcement

Violation of this Order may result in any of the actions specified in section 210.75 of the Commission's Rules of Practice and Procedure (19 C.F.R. § 210.75), including an action for civil penalties under section 337(f) of the Tariff Act of 1930 (19 U.S.C. § 1337(f)), as well as any other action that the Commission deems appropriate. In determining whether Respondent is in violation of this Order, the Commission may infer facts adverse to Respondent if it fails to provide adequate or timely information.

# X. Modification

The Commission may amend this Order on its own motion or in accordance with the procedure described in section 210.76 of the Commission's Rules of Practice and Procedure (19 C.F.R. § 210.76).

# XI. Bonding

The conduct prohibited by Section III of this Order may be continued during the sixty-day period in which this Order is under review by the United States Trade Representative, as delegated by the President (70 FR 43251 (July 21, 2005)), subject to the Respondent's posting of

a bond in the amount of zero (0) percent of the entered value of the covered products. This bond provision does not apply to conduct that is otherwise permitted by section IV of this Order. Covered products imported on or after the date of issuance of this Order are subject to the entry bond set forth in the exclusion order issued by the Commission, and are not subject to this bond provision.

By order of the Commission.

Lisa R. Barton

Secretary to the Commission

Issued: August 22, 2018

# CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

# PUBLIC CERTIFICATE OF SERVICE

I, Lisa R. Barton, hereby certify that the attached **ORDER** has been served by hand upon the Commission Investigative Attorney, Yoncha L. Kundupoglu, Esq., and the following parties as indicated, on 8/22/2018

Lisa R. Barton, Secretary U.S. International Trade Commission 500 E Street, SW, Room 112 Washington, DC 20436

# On Behalf of Complainants: Michael T. Renaud, Esq. ☐ Via Hand Delivery MINTZ LEVIN COHN FERRIS GLOVSKY AND POPEO PC ☑ Via Express Delivery One Financial Center ☐ Via First Class Mail Boston, MA 02111 ☐ Other: On Behalf of Respondents VIZIO, Inc.: Cono A. Carrano, Esq. ☐ Via Hand Delivery AKIN GUMP STRAUSS HAUER & FELD LLP Robert S. Strauss Building ☐ Via First Class Mail 1333New Hampshire Avenue, NW ☐ Other: Washington, DC 20036 On Behalf of Respondents MediaTek, Inc., MediaTek USA Inc., and Sigma Designs, Inc.: Tyler T. VanHoutan, Esq. ☐ Via Hand Delivery MCGUIREWOODS LLP ☑ Via Express Delivery 600 Travis Street, Suite 7500 ☐ Via First Class Mail Houston, TX 77002 ☐ Other:

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN GRAPHICS SYSTEMS, COMPONENTS THEREOF, AND CONSUMER PRODUCTS CONTAINING THE SAME

Inv. No. 337-TA-1044

# **COMMISSION OPINION**

On April 13, 2018, the presiding Administrative Law Judge ("ALJ") in the above-identified investigation issued her final initial determination ("FID") finding a violation of section 337 of the Tariff Act of 1930, as amended, 19 U.S.C. § 1337 ("section 337"), by Respondents VIZIO, Inc. ("VIZIO"), MediaTek Inc. and Media Tek USA Inc. (collectively, "MediaTek"), and Sigma Designs, Inc. ("SDI"). Having considered the FID, the parties' petitions, responses, and written submissions, and the record in this investigation, the Commission has determined to affirm the FID's ultimate conclusions of a section 337 violation with respect to U.S. Patent No. 7,633,506 ("the '506 patent") and no section 337 violation with respect to U.S. Patent No. 7,796,133 ("the '133 patent"). The Commission has also determined to modify the FID's analysis in part as explained below. All findings in the FID that are consistent with this opinion are affirmed.

# I. BACKGROUND

# A. Procedural Background

By publication in the Federal Register on March 22, 2017, the Commission instituted this investigation based on a complaint filed by Complainants Advanced Micro Devices, Inc. of Sunnyvale, California and ATI Technologies ULC of Markham, Ontario (collectively, "AMD"

or "Complainants"). See 82 Fed. Reg. 14748 (Mar. 22, 2017). The complaint, as amended, alleges violations of section 337 of the Tariff Act of 1930, as amended (19 U.S.C. § 1337), based upon the importation into the United States, the sale for importation, and the sale within the United States after importation of certain graphics systems, components thereof, and consumer products containing the same by reason of infringement of claims 1-9 of the '506 patent; claims 1-13 and 40 of the '133 patent; claims 2-5, 6-10, and 11 of U.S. Patent No. 8,760,454 ("the '454 patent"); and claims 1-8 of U.S. Patent No. 9,582,846 ("the '846 patent"). See id.

In addition to VIZIO, MediaTek, and SDI, the notice of investigation identified LG Electronics, Inc., LG Electronics U.S.A., Inc., and LG Electronics MobileComm U.S.A. Inc. (collectively, "LG") as respondents in this investigation. *See id.* The Office of Unfair Import Investigations is also a party to the investigation. *See id.* On October 20, 2017, the ALJ issued an initial determination terminating the investigation as to LG based on settlement. *See* Order No. 48 (Oct. 20, 2017), *unreviewed*, Comm'n Notice (Nov. 13, 2017).

The ALJ also terminated the investigation with respect to all asserted claims of the '454 and '846 patents; claims 6, 7, and 9 of the '506 patent; and claims 2, 4-13, and 40 of the '133 patent. See Order No. 33 (Aug. 15, 2017), unreviewed, Comm'n Notice (Sept. 5, 2017); Order No. 43 (Oct. 5, 2017), unreviewed, Comm'n Notice (Oct. 31, 2017); Order No. 49 (Oct. 20, 2017), unreviewed, Comm'n Notice (Nov. 13, 2017); Order No. 53 (Oct. 31, 2017), unreviewed, Comm'n Notice (Nov. 28, 2017). Claims 1-5 and 8 of the '506 patent and claims 1 and 3 of the '133 patent (hereinafter, "the asserted claims") remain pending in this investigation.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup> "Respondents," hereinafter, means VIZIO, MediaTek, and SDI.

<sup>&</sup>lt;sup>2</sup> "Asserted patents," hereinafter, means the '506 and '133 patents.

On September 28, 2017, AMD filed an unopposed motion for summary determination that it satisfied the economic prong of the domestic industry requirement ("Domestic Industry Motion," EDIS Doc. No. 624231). The ALJ did not issue a ruling on AMD's Domestic Industry Motion. On October 26, 2017, the parties filed a joint stipulation in which Respondents agreed that AMD satisfied both the economic and technical prongs of the domestic industry requirement. *See* JX-9C, Stipulation on Domestic Industry. AMD and VIZIO also filed a joint stipulation concerning importation and inventory on November 6, 2017. *See* JX-10C, Stipulation on Importation and Inventory.

On November 8, 2017, the ALJ held a telephonic conference during which she provided her rulings with respect to the level of skill in the art and the constructions of the disputed claim terms. *See* November 8, 2017 Teleconference Tr., EDIS Doc. No. 629745 ("Markman Order Tr.").

The ALJ conducted an evidentiary hearing from November 27, 2017 through December 1, 2017,<sup>3</sup> and on April 13, 2018, the ALJ issued her FID finding a violation of section 337. Specifically, the FID finds that: (1) certain accused products infringe the '506 patent but not the '133 patent; (2) the asserted claims are not invalid; and (3) Complainants satisfy the economic and technical prongs of the domestic industry requirement with respect to both asserted patents. In addition, the ALJ issued a Recommended Determination ("RD") recommending that the Commission issue: (1) a limited exclusion order ("LEO") against the infringing accused products; and (2) CDOs against Respondents VIZIO and SDI. The ALJ further recommended against setting a bond during Presidential review. On April 27, 2018, the ALJ issued errata to correct clerical errors in the FID.

<sup>&</sup>lt;sup>3</sup> The transcript of the evidentiary hearing is referred to, hereinafter, as "Hearing Tr."

On April 30, 2018, Respondents filed a petition for review of the FID ("Respondents' Pet.") and Complainants filed a contingent petition for review ("Complainants' Pet."). On May 8, 2018, the parties filed responses to each other's petition (referred to, hereinafter, as "Complainants' Pet. Resp.," "Respondents' Pet. Resp.," and "IA's Pet. Resp.").

On June 14, 2018, the Commission issued a Notice determining to review the FID in part. See 83 Fed. Reg. 28660-62 (June 20, 2018). Specifically, the June 14, 2018 Notice provided that:

[T]he Commission has determined to review the claim constructions of the terms: "unified shader" (recited in the '506 and '133 patent claims), "packet" (recited in the '133 patent claims), and "ALU/memory pair" (recited in the '133 patent claims). In view of the Commission's claim construction review, the Commission will also review the relevant FID's findings with respect to infringement, validity, and technical prong of the domestic industry requirement. Furthermore, the Commission has determined to review whether the importation requirement is satisfied with respect to Respondents MediaTek and SDI. The Commission has determined not to review the remainder of the FID.

See id. In addition, the June 14, 2018 Notice proposed constructions for the claim terms under review as follows: (1) unified shader: a single shader circuit capable of performing color shading and texture coordinate shading, wherein the single shader circuit may not include separate dedicated hardware blocks that perform separate color and texture operations, and wherein texture coordinate shading may include texture address operations, indirect texturing, and bump mapping performed by the unified shader to modify texture coordinates; (2) packet: data bundle containing texture coordinate and color value information for one or more pixels, wherein said information is received simultaneously by the unified shader; and (3) ALU/memory pair: does not exclude control logic or circuitry. See id. Furthermore, the June 14, 2018 Notice requested

<sup>&</sup>lt;sup>4</sup> "IA" means the Commission's Investigative Attorney.

briefing in response to certain questions relating to the claim constructions under review. See id. The Commission also solicited written submissions on the issues of remedy, the public interest, and bonding. See id.

On June 28, 2018, the parties filed written submissions in response to the June 14, 2018 Notice ("Complainants' Suppl. Br.," "Respondents' Suppl. Br.," and "IA's Suppl. Br."), and on July 6, 2018, the parties filed responses to each other's submissions ("Complainants' Suppl. Resp.," "Respondents' Suppl. Resp.," and "IA's Suppl. Resp.").

On June 26, 2018, Complainants filed a motion for leave to amend the complaint and notice of investigation to add V-Silicon Inc. and V-Silicon International, Inc. (collectively, "V-Silicon") as Respondents in this Investigation and a memorandum in support thereof ("Mem."). On July 5 and 6, 2018, the IA and Respondents, respectively, filed responses to Complainants' motion to amend ("IA's Mem. Resp." and "Respondents' Mem. Resp.").

# B. The Asserted Patents

# 1. The '506 Patent

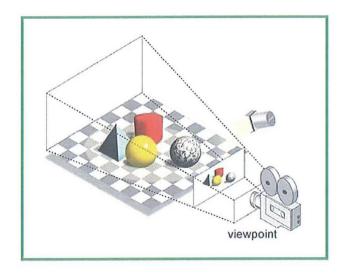

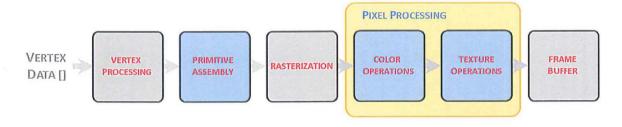

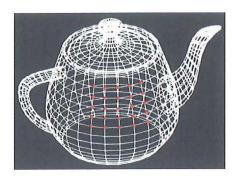

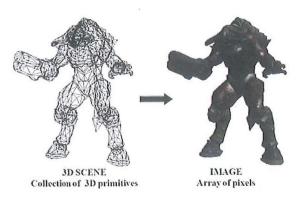

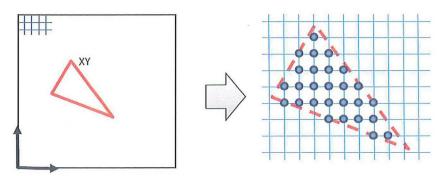

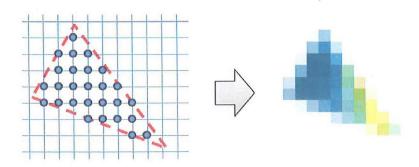

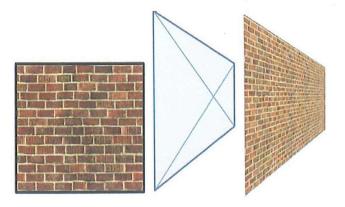

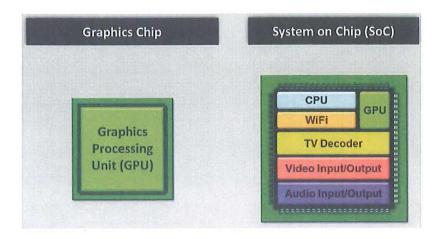

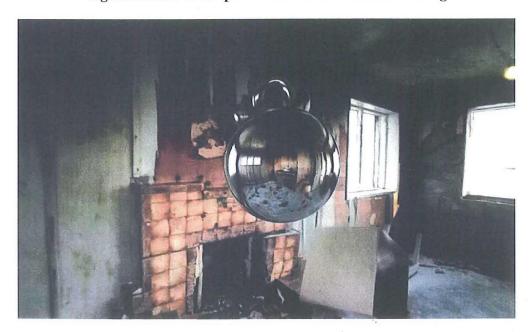

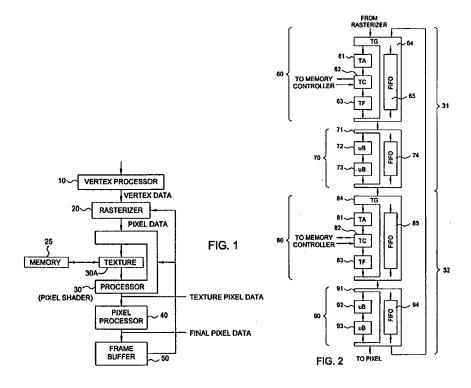

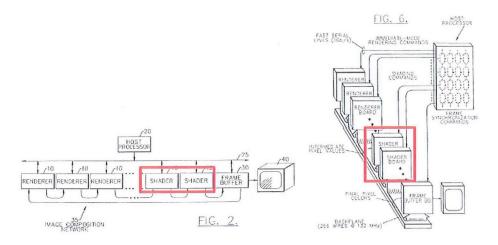

The '506 patent, titled "Parallel Pipeline Graphics System," issued on December 15, 2009, and claims priority to a provisional patent application filed on November 27, 2002. The '506 patent generally relates to "[a] parallel pipeline graphics system includ[ing] a back-end configured to receive primitives and combinations of primitives (*i.e.*, geometry) and process the geometry to produce values to place in a frame buffer for rendering on screen." *See JX-1*, '506 patent at Abstract. The '506 patent explains that "[g]raphics chips are specifically designed to handle the complex and tedious instruction processing that must be used to render the graphics to the screen." *Id.* at 2:17-19. The '506 patent also explains that "[g]raphics chips have a frontend and a back-end," "[t]he front-end typically receives graphics instructions and generates the

primitives or combination of primitives that define geometric patterns," and "[t]he primitives are then processed by the back end where they might be textured, shaded, colored, or otherwise prepared for final output." *Id.* at 2:19-26. The '506 patent further states that "[m]odern graphics processing chip back-ends are equipped to handle three-dimensional data," but "[w]hen processing three-dimensional data, memory bandwidth becomes a limitation on performance." *Id.* at 2:32-36. "Unlike prior single pipeline implementation," the '506 patent continues, "some embodiments use two or four parallel pipelines" and "[w]hen geometry data is sent to the back-end, it is divided up and provided to one of the parallel pipelines." *Id.* at 2:49-58, Abstract.

Independent claim 1 of the '506 patent recites:

# 1. A graphics chip comprising:

a front-end in the graphics chip configured to receive one or more graphics instructions and to output a geometry;

a back-end in the graphics chip configured to receive said geometry and to process said geometry into one or more final pixels to be placed in a frame buffer;

wherein said back-end in the graphics chip comprises multiple parallel pipelines;

wherein said geometry is determined to locate in a portion of an output screen defined by a tile; and

wherein each of said parallel pipelines further comprises a unified shader that is programmable to perform both color shading and texture shading.

# 2. The '133 Patent

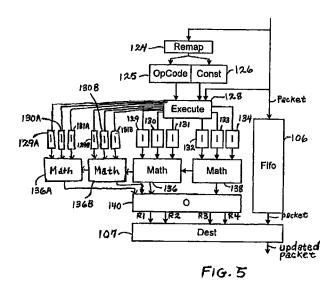

The '133 patent, titled "Unified Shader," issued on September 14, 2010, and relates to a provisional patent application filed on November 18, 2002 (earliest priority date). The '133 patent generally relates to "a unified shader unit used in texture processing in graphics processing device." *See* JX-3, '133 patent at Abstract. The '133 patent states that "[u]nlike the

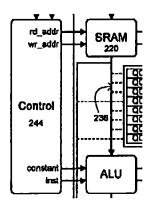

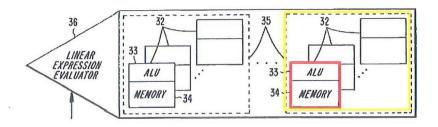

conventional method of using one shader for texture coordinate shading and another for color shading, the present shader performs both operations" and "uses the same precision for both texture coordinate and color shading, thus simplifying the complexity of programming for two separate conventional shaders with different levels of precision." *Id.* The '133 patent explains that "[i]n prior art systems, indirect texture and bump mapping would have required large FIFO<sup>5</sup> memory structures" while "[t]he unified shader in the present invention handles such mapping without the huge FIFOs and buffer register needed in a conventional texture shader." *Id.* at 3:46-50. For example, the '133 patent provides that "the internal clock scheduling mechanism and architecture ALU/SRAM pairs of the unified shader enable it to use only a single memory structure, which may be a FIFO." *Id.* at 3:50-53. The '133 patent further states that "because the buffer register is not needed in the FIFO of the unified shader, the cost associated with synchronizing between a buffer register and a FIFO is removed." *Id.* at 3:56-58.

Independent claim 1 of the '133 patent recites:

# 1. A unified shader comprising:

an input interface for receiving a packet from a rasterizer;

a shading processing mechanism configured to produce a resultant value from said packet by performing one or more shading operations, wherein said shading operations comprise both texture operations and color operations and comprising at least one ALU/memory pair operative to perform both texture operations and color operations wherein texture operations comprise at least one of: issuing a texture request to a texture unit and writing received texture values to the memory and wherein the at least one ALU is operative to read from and write to the memory to perform both texture and color operations; and

an output interface configured to send said resultant value to a frame buffer.

<sup>&</sup>lt;sup>5</sup> "FIFO" refers to "first-in, first-out . . . memory structure." See JX-3, '133 patent at Abstract.

# C. The Domestic Industry Products

The FID describes AMD's domestic industry products as: (1) the Single Shader Products; and (2) the Multi Shader Products. *See* FID at 30. The FID further states that the domestic industry products contain a GFX 8, GFX 8.1, or GFX 9 graphics processing unit ("GPU"). *See id.* The FID finds that the Single Shader Products practice claims 1 and 8 of the '506 Patent and claims 1 and 3 of the '133 Patent, while AMD's Multi Shader Products practice claims 1-5 and 8 of the '506 Patent and claims 1, 3, and 8 of the '133 Patent. *See id.* at 132-33.

# D. The Accused Products

The FID describes the accused products as those products incorporating the Utgard GPU design from third-party ARM Holdings ("ARM"). See FID at 26. Specifically, the Utgard GPUs at issue in this investigation are: (1) [

] ("the Singlepipe Utgard GPU"); and (2) the ARM Mali 400 [ ] MPx<sup>6</sup> models, [ ] ("the Multipipe Utgard GPUs"). See id. at 26-27.

More specifically, the accused Singlepipe products include MediaTek's [

], and VIZIO's products (i.e., televisions) that

incorporate accused MediaTek's Singlepipe IC. See id. at 27, 29. And the accused Multipipe products include MediaTek's ICs [

]; SDI's ICs [

<sup>&</sup>lt;sup>6</sup> "MPx" refers to GPU configurations having more than one [ ] (e.g., ARM Mali 400/[] MP2 or ARM Mali 400/[] MP4) as distinguished from the MP1 model, which contains only one [ ] (e.g., ARM Mali 400 MP1).

]; and VIZIO's televisions that incorporate MediaTek's and SDI's accused Multipipe ICs. See id. at 27-30.

AMD argues that the Singlepipe Utgard GPU infringes claims 1 and 3 of the '133 patent and the Multipipe Utgard GPUs infringe all of the asserted claims of both the '506 and '133 patents. *See id.* at 27.

# II. STANDARD ON REVIEW

Commission Rule 210.45(c) provides that "[o]n review, the Commission may affirm, reverse, modify, set aside or remand for further proceedings, in whole or in part, the initial determination of the administrative law judge" and that "[t]he Commission also may make any findings or conclusions that in its judgment are proper based on the record in the proceeding."

See 19 C.F.R. § 210.45(c). In addition, as explained in Certain Polyethylene Terephthalate

Yarn and Products Containing Same, "[o]nce the Commission determines to review an initial determination, the Commission reviews the determination under a de novo standard." Inv. No. 337-TA-457, Comm'n Op., 2002 WL 1349938, \*5 (June 18, 2002) (citations omitted). This is "consistent with the Administrative Procedure Act which provides that once an initial agency decision is taken up for review, 'the agency has all the powers which it would have in making the initial decision except as it may limit the issues on notice or by rule." Id. (citing 5 U.S.C. § 557(b)).

# III. <u>DISCUSSION</u>

As discussed *supra* section I(A), the Commission determined to review whether the importation requirement is satisfied with respect to Respondents MediaTek and SDI. *See* 83 *Fed. Reg.* 28660-62 (June 20, 2018). In addition, the Commission determined to review the claim constructions of the terms: "unified shader" (recited in the '506 and '133 patent claims),

"packet" (recited in the '133 patent claims), and "ALU/memory pair" (recited in the '133 patent claims). See id. Furthermore, in view of the Commission's claim construction review, the Commission also determined to review the FID's relevant findings with respect to infringement, validity, and technical prong of the domestic industry requirement. See id. The Commission has determined not to review the remainder of the FID and such findings have thus become the determination of the Commission. See 19 C.F.R. § 210.42(h)(2).

# A. Importation

The Commission finds that the record evidence establishes that the importation requirement is satisfied for both MediaTek and SDI.

In particular, the Commission finds that MediaTek and SDI did not simply place their respective products into the stream of commerce with no knowledge that they would be imported into the United States. See Certain Erasable Programmable Read Only Memories, Components Thereof, Prods. Containing Such Memories, and Processes for Making Such Memories, Inv. No. 337-TA-276, Initial Determination, 1988 WL 1524737, at \*14 (Nov. 16, 1988), unreviewed in relevant part, Comm'n Notice, 54 Fed. Reg. 1011-01, 1989 WL 271090 (Jan. 11, 1989) (finding the importation requirement satisfied where respondent took "actions . . . purposefully directed to the United States" and "has done much more than simply place its . . . products into the stream of commerce"); compare Certain Integrated Circuits, Processes for Making Same, and Prods. Containing Same, Inv. No. 337-TA-450, Order No. 15, Initial Determination, 2001 WL 1598072, at \*4 (Nov. 2, 2001), unreviewed, Comm'n Notice, 2001 WL 1563177 (Dec. 5, 2001) ("Standing alone, placement of a product in the stream of commerce is not sufficient to establish importation.").

MediaTek and SDI knew that their respective accused GPUs would subsequently be imported into the United States by VIZIO. See Certain Inkjet Ink Cartridges with Printheads & Components Thereof, Inv. No. 337-TA-723, Initial Determination, 2011 WL 3489151 (June 10, 2011) ("With regard to a 'sale for importation,' a complainant must prove that a respondent sold infringing articles and knew or should have known that those articles would be subsequently exported to the United States") (citation omitted), aff'd in relevant part, Comm'n Op. (Dec. 1, 2011); accord IA's Pet. Resp. at 10-11. VIZIO is one of the largest television providers in the U.S. market (see RX-543) and MediaTek and SDI are VIZIO's [ ] providers of GPUs (see CX-3879C, VIZIO's Interrog. Resps.). The VIZIO accused products are [

]. See JX-10C, Stipulation on Importation and Inventory at JX-10C.20.

MediaTek knows that [

]. See CX-3848C, MediaTek's Interrog.

Resps. at CX-3848C.19 ("[I]t is MediaTek's understanding that the information sought in this Interrogatory<sup>7</sup> [

]"); CX-129C, Hwang<sup>8</sup> Dep. Tr. at 21:1-24. SDI similarly [

]

<sup>&</sup>lt;sup>7</sup> The relevant Interrogatory requests information on "the first projected quarter in which the MediaTek Future Product will be: (a) imported, sold for importation, and/or sold within the United States after importation, into the United States; and (b) marketed, advertised, announced, or promoted for importation, sale for importation, and/or sale in the United States." See CX-3848C.18.

<sup>&</sup>lt;sup>8</sup> Mr. John Hwang is VIZIO's Rule 30(b)(6) witness (corporate representative).

the United States." *See* CX-135C; CX-129C, Hwang Dep. Tr. at 23:21-25, 39:23-41:23. Thus, MediaTek and SDI did not merely place their respective products into the stream of commerce but knew and participated in VIZIO's importation and sale of infringing articles in the United States. As such, the importation requirement is satisfied as to Respondents MediaTek and SDI.

Thus, the Commission has determined to affirm the FID's findings that Complainants satisfy the importation requirement as to MediaTek and SDI, and the Commission supplements the FID's analysis as provided above.

# B. The '506 Patent

# 1. <u>Claim Construction</u>

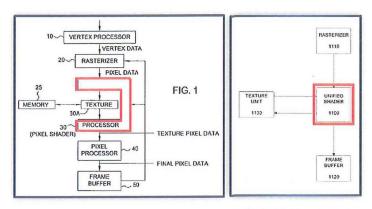

The Commission has determined to review the FID's claim construction for the term "unified shader" and to clarify that the term means "a single shader circuit capable of performing color shading and texture coordinate shading, wherein the single shader circuit may not include a circuit having separate dedicated hardware blocks that perform separate color shading and texture coordinate shading, and wherein texture coordinate shading may include texture address operations, indirect texturing, and bump mapping performed by the unified shader to modify texture coordinates."

The FID construes "unified shader" as "a single shader circuit capable of performing color shading and texture coordinate shading." See FID at 40 (citing Markman Order Tr.).

Respondents fault the FID for expanding the scope of the term "unified shader," to include "multiple components or units [that] can perform color and texture operations, as long as these components or units are within the same electronic loop." See Respondents' Pet. at 14.

Respondents contend that the FID's "finding that a 'unified shader' can be comprised of 'multiple components or units to perform color and texture operations, as long as these

components or units are within the same electronic loop'... is erroneous in light of th[e] clear disavowal of claim scope during prosecution [over Zhu U.S. Patent No. 6,697,063]." See id. at 15-16 (citing FID at 58; JX-2, '506 Patent Prosecution File at JX-2.387-388). According to Respondents, "Figure 17 of Zhu clearly shows that the color, texture, and other blocks [are] part of the 'same electronic loop.'" See id. at 16 n.11. Complainants respond that "the multiple subcomponents of the unified shader make up a 'single shader circuit' because color shading and texture coordinate shading are not performed in separate circuits," i.e., "the internal circuitry of each of the [unified shader] boxes participates in providing the capability of performing both color shading and texture coordinate shading." See Complainants' Pet. Resp. at 16.

The construction of the claim term "unified shader" may not encompass prior art embodiments, which were distinguished and therefore disclaimed during prosecution. See Edwards Lifesciences LLC v. Cook Inc., 582 F.3d 1322, 1333 (Fed. Cir. 2009) ("[I]n attempting to distinguish claims without an express malleable wire limitation over certain prior art, [the patentee] stated that the written description 'expressly teaches that the wire forms are malleable, deformable, non-springy material' and that they are not 'self-expanding.' . . . [The patentee] cannot now reclaim what it disclaimed during prosecution and throughout the specification, viz., resilient wires."); Rheox, Inc. v. Entact, Inc., 276 F.3d 1319, 1326 (Fed. Cir. 2002) (finding that the patentee relinquished a particular claim construction based on the totality of the prosecution history, including amendments to claims and arguments made to overcome or distinguish references). In particular, the patentee stated during the prosecution of the '506 patent:

As set forth in paragraph 53 and elsewhere in the Specification, unlike Zhu the claimed unified shader is operative to apply a program sequence of executable instructions to rasterized values and is operative to perform both color shading and/or texture shading. No such structure is set forth in the cited portion of the Zhu reference. Instead the Zhu reference utilizes separate dedicated

hardware blocks as shown to perform separate color and texture interpolation operations.

See JX-2, '506 Patent Prosecution History at JX-2.387-388. Thus, the "unified shader" claim term may not broadly encompass an embodiment wherein distinct components or units perform either color shading or texture coordinate shading as long as these components or units are within the same electronic loop. Such construction would encompass the Zhu prior art embodiment which was expressly distinguished and disclaimed during prosecution.

However, contrary to Respondents' assertions, it does not appear that the FID applied the broad construction that was disclaimed during prosecution. Rather, in stating that "multiple components or units can perform color and texture operations, as long as these components or units are within the same electronic loop," the FID was rejecting Respondents' argument that the claimed unified shader refers to a single component. See FID at 57-58. And the FID applied a "single shader circuit" construction which, consistent with the patentee's disclaimer during prosecution, excludes an embodiment wherein separate dedicated hardware blocks perform separate color shading and texture coordinate shading. See, e.g., FID at 79 (rejecting invalidity claim over prior art in which "shading and texturing operations are performed by separate hardware components or circuits"); compare id. at 53, 59 (finding that [

] components of the accused unified

<sup>&</sup>lt;sup>9</sup> For example, Respondents do not explain in what way the accused products are similar to the disclaimed embodiment of Zhu, and Respondents do not identify components of the accused unified shader that separately performs color shading or texture coordinate shading. While Respondents argue that "the [ ]," there is no requirement for the unified shader to generate texture coordinates but rather, "texture coordinate shading . . . involves modifying texture coordinates after the texture coordinates are generated." See FID at 62; see also id. ("[T]he rasterizer, not the unified shader, produces the texture coordinates, and . . . the unified shader applies texturing instructions to the rasterized texture coordinates.") (citing JX-1, '506 patent at 6:38-49); compare id. at 59 ("The Utgard GPU contains a [ ].").

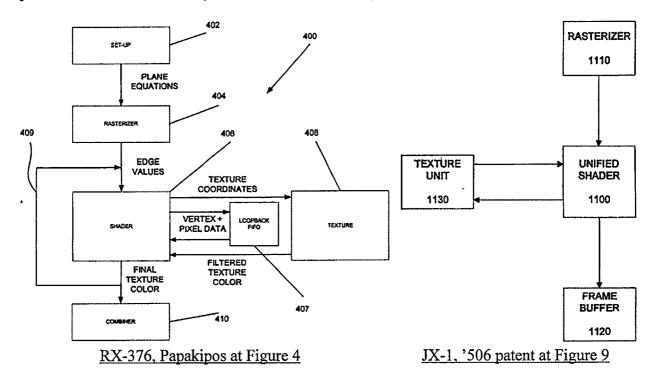

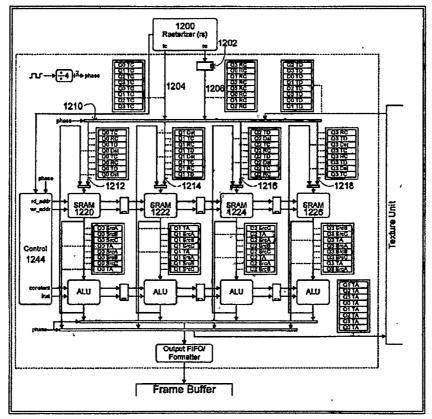

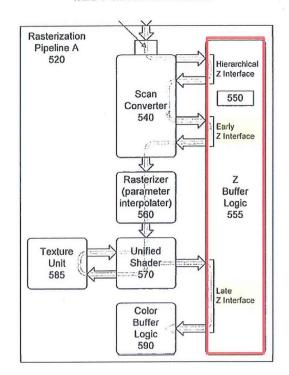

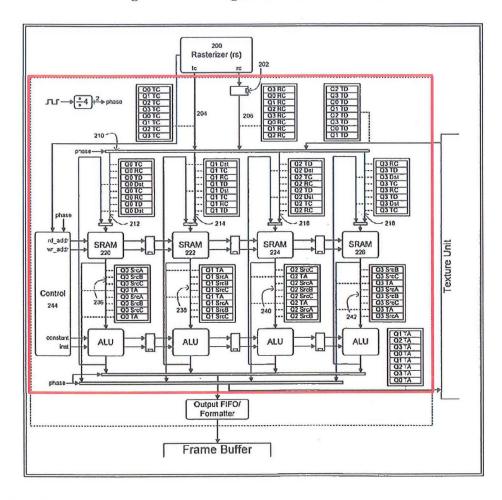

shader performs both color shading and texture coordinate shading). This is also consistent with the '506 patent specification which "shows a unified shader architecture according to an embodiment of the present invention" wherein the "unified shader" may include multiple components such as a "control logic block 1244" and "SRAM/ALU pairs 1220, 1222, 1224, and 1226," and those components participate in performing both color and texture coordinate (texture address<sup>10</sup>) shading. *See* JX-1, '506 patent at Figure 10, 3:39-40, 9:60-10:22; *see also id.* 6:53-57 ("The conventional distinction between shading operations (i.e., color texture map and coordinate texture map or color shading operation and texture address operation) is not handled by the use of separate shaders."); *accord* Complainants' Suppl. Br. at 6; *accord* IA's Suppl. Br. at 10-11.<sup>11</sup>

The Commission also finds that the FID correctly determined that "texture coordinate shading" is required in the construction of the term "unified shader," and the Commission further clarifies that "texture coordinate shading" may include texture address operations, indirect

As explained *infra*, the '506 patent specification uses "texture address shading" and "texture coordinate shading" interchangeably. *See also* Complainants' Claim Construction Br. at 61 (EDIS Doc. No. 617784) ("In the '506 patent specification, the patentee uses the terms 'texture coordinate shading' and 'texture address shading' interchangeably to show that 'texture coordinate/address shading' are encompassed by 'texture shading. . . . Indeed, the disclosure equates 'texture coordinates' with 'texture addresses.'").

The unified shader may also include separate hardware components for performing functions other than color shading or texture coordinate shading, e.g.: "(a) block 1202 . . . that is separate and dedicated to delaying only color values but not texture coordinates; (b) wire 1204 that is separate and dedicated to carrying only color values but not texture coordinates; and (c) wire 1206 that is separate and dedicated to carrying only texture coordinates but not color values." See Complainants' Suppl. Br. at 5 (citing JX-1, '506 patent at Figure 10).

texturing, and bump mapping performed by the unified shader to modify texture coordinates. <sup>12</sup> The '506 patent specification makes clear that "[t]he unified shader performs both color shading and texture address shading." *See* JX-1, '506 patent at 6:52-53. The '506 patent specification states that:

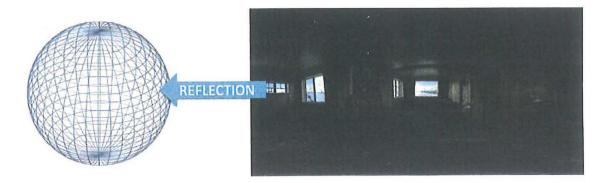

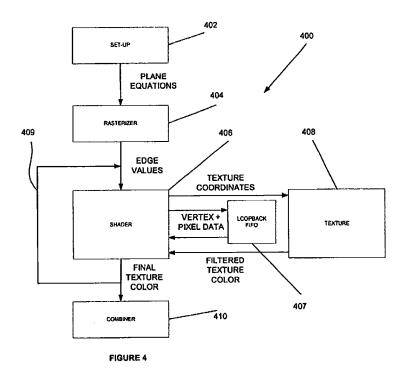

A unified shader 570 works in conjunction with the texture unit 585 and applies a programmed sequence of instructions to the rasterized These instructions may involve simple mathematical values. functions (add, multiply, etc.) and may also involve requests to the texture unit. A unified shader reads in rasterized texture addresses and colors, and applies a programmed sequence of instructions. A unified shader is so named because the functions of a traditional color shader and a traditional texture address shader are combined into a single, unified shader. 13 The unified shader performs both color shading and texture address shading. The conventional distinction between shading operations (i.e., color texture map and coordinate texture map or color shading operation and texture address operation) is not handled by the use of separate shaders. In this way, any operation, be it for color shading or texture shading. may loop back into the shader and be combined with any other operation.

The functionality of a unified shader is further described in commonly owned co-pending U.S. patent application entitled

<sup>&</sup>quot;[T]exture coordinate shading is a subset of texture shading . . . . [S]hading is changing or manipulating a value, right." Hearing Tr. at 444:11-20 (Reinman); *id.* at 1169:12-18 (Edwards) ("[C]olor shading and texture coordinate shading . . . are types of color and texture operations, respectively."); *see also* FID at 23 ("An example of texture coordinate shading is the depiction of reflections in irregular objects, such as reflections in a pond in which the water is moving and the reflected texture changes over time.") (citing Hearing Tr. at 1377:15-1378:7 (Wolfe)); *id.* at 58 ("[E]xperts for both Complainants and Respondents agreed that texture coordinate shading is a more complex texture shading operation than texture mapping, which involves modifying texture coordinates once they are generated.") (citations omitted); Hearing Tr. at 1090:2-4 (Edwards) ("[T]exture coordinate shading is the ability to take . . . [t]exture coordinates and modify them."); JX-3, '133 patent at 2:58-61 ("[T]exture coordinate shaders have been limited to only performing high precision bump mapping displacement algorithms").

<sup>&</sup>lt;sup>13</sup> This statement explicitly defines the "unified shader" as performing the functions of a traditional color shader and a traditional texture address shader (*i.e.*, texture coordinate shader), and shows that the patentee acted as its own lexicographer. See Edwards Lifesciences, 582 F.3d at 1329.

"Unified Shader," with Ser. No. 10/730,965, filed Dec. 8, 2003 [(the '133 patent)], and is hereby fully incorporated by reference.

See JX-1, '506 patent at 6:43-63. The '133 patent specification, which is "fully incorporated by reference" into the '506 patent specification, similarly provides that:

The unified shader performs both color shading and texture coordinate shading. The unified shader takes a relatively high numerical precision like a texture coordinate shader, but uses the same precision for color shading. The conventional distinction between shading operations (i.e., color texture map and coordinate texture map or color shading operation and texture coordinate operation) is not handled by the use of separate shaders. In the present invention, such distinction is only the intent of the application and the application program interface (API). In this way, any operation, be it for color shading or texture shading, may loop back into the shader and be combined with any other operation.

See JX-3, '133 patent at 3:18-29; see also id. at Abstract ("The present invention is a unified shader unit used in texture processing in graphics processing device. Unlike the conventional method of using one shader for texture coordinate shading and another for color shading, the present shader performs both operations.").

In their claim construction briefing, Complainants acknowledged that texture coordinate shading can include texture address operations, indirect texturing, and bump mapping (provided texture coordinates are modified). See Complainants' Claim Construction Br. at 13 (EDIS Doc. No. 617784) ("[A] 'texture coordinate shader[]' is used to execute texture coordinate threads to, for example, alter the texture coordinates of a pixel in indirect texturing or perform bump mapping."); id. at 23 ("The conventional wisdom in the graphics processing industry was to employ highly specialized and dedicated circuitry for (1) modifying textures, via processes such as bump mapping and indirect texturing, and calculating perspective correct texture coordinates."); id. at 61 ("In the '506 patent specification, the patentee uses the terms 'texture coordinate shading' and 'texture address shading' interchangeably to show that 'texture

coordinate/address shading' are encompassed by 'texture shading. . . . Indeed, the disclosure equates 'texture coordinates' with 'texture addresses.'"); *id.* ("The '506 patent specification further supports that 'indirect texturing' and bump mapping (coordinate texture mapping) are accomplished by executing texture coordinate/address operations."); *id.* at 63 ("[B]ump mapping is accomplished by altering texture coordinates which is done by 'texture coordinate operations.' . . . [S]ince bump mapping is an indirect texturing operation, indirect texturing includes 'texture coordinate operations.'") (citing '133 patent at 2:30-42). Thus, "texture coordinate shading" broadly means any modification to texture coordinates, which can be accomplished by the unified shader through indirect texturing, bump mapping, or texture address operations. <sup>14</sup>

\*\*Accord\*\* IA's Suppl. Br. at 12.

Respondents argue that texture coordinate shading is not required in the construction of "unified shader." See, e.g., Respondents' Suppl. Br. at 2. In particular, Respondents cite to a recent decision by the Patent Trial and Appeal Board's ("PTAB") to institute inter partes review proceedings for the '506 patent. See id. at 2 n.1; Respondents' Pet. at 19 n.14. Respondents note that the PTAB reaches a different conclusion with respect to the construction of a "unified shader," and states that "the term 'texture coordinate shading'... is not used, much less defined in the '506 patent." See Respondents Suppl. Br. at 2 n.1; PTAB Decision at 14 (Apr. 27, 2018) (EDIS Doc. No. 643698). As noted above, however, the '506 patent specification explicitly provides that "Itlhe unified shader performs ... texture address shading," a term used

<sup>&</sup>lt;sup>14</sup> Complainants' argument that "texture coordinate shading can, but is not required to, be used during texture address operations, bump-mapping, and indirect texturing" (*see* Complainants' Suppl. Br. at 13) is not inconsistent with the Commission's construction. *Accord* IA's Suppl. Resp. at 7 ("[T]he use of 'may' in the Commission's construction adequately addresses the fact that texture address operations, indirect texturing, and bump mapping can, but need not involve, texture coordinate operations.").

interchangeably with "texture coordinate shading" in the '506 patent. See, e.g., Complainants' Claim Construction Br. at 61. And Respondents' expert testified that "texture address operations and texture coordinate shading or texture coordinate operations are equivalent" and that "[his] understanding is that AMD agrees with [him] on this." See Hearing Tr. at 995:19-22 (Edwards<sup>15</sup>); see also id. at 444:21-445:8 (Reinman<sup>16</sup>) ("[T]exture address calculations [are] akin to texture coordinate shading. [T]exture coordinates . . . are provided to the texture unit [while] the addresses . . . are in memory. . . . [Y]ou perform a texture address operation . . . through texture coordinate shading."); JX-1, '506 patent at 11:15-17 ("Each pixel contains one or more sets of texture coordinates (texture addresses), and one or more color values.").

Furthermore, the '506 patent specification explicitly incorporates the '133 patent disclosure and states that the functionality of the unified shader is further described therein.

Therefore, the construction of "unified shader" should be also based on the disclosure of the '133 patent. See Paice LLC v. Ford Motor Company, 881 F.3d 894, 906-07 (Fed. Cir. 2018).

Thus, the Commission has determined on review to modify the FID's construction of the term "unified shader" and to construe such term to mean "a single shader circuit capable of performing color shading and texture coordinate shading, wherein the single shader circuit may not include a circuit having separate dedicated hardware blocks that perform separate color

<sup>&</sup>lt;sup>15</sup> Dr. Stephen Edwards is Respondents' expert on invalidity of the '506 and '133 patents.

<sup>&</sup>lt;sup>16</sup> Dr. Glenn Reinman is AMD's technical expert on infringement.

shading and texture coordinate shading,<sup>17</sup> and wherein texture coordinate shading may include texture address operations, indirect texturing, and bump mapping performed by the unified shader to modify texture coordinates."

#### 2. Infringement

AMD asserted that the Multipipe Utgard GPUs infringe claims 1-5 and 8 of the '506 patent. In light of the Commission's review of the FID's claim construction of the term "unified shader," discussed *supra* section III(B)(1), the Commission also determined to review the FID's relevant infringement findings. *See* 83 *Fed. Reg.* 28660-62 (June 20, 2018).

## (i) Claim 1

Claim 1 of the '506 patent recites:

[1pre] A graphics chip comprising:

[1a] a front-end in the graphics chip configured to receive one or more graphics instructions and to output a geometry;

[1b] a back-end in the graphics chip configured to receive said geometry and to process said geometry into one or more final pixels to be placed in a frame buffer;

[1c] wherein said back-end in the graphics chip comprises multiple parallel pipelines;

[1d] wherein said geometry is determined to locate in a portion of an output screen defined by a tile; and

While the June 14, 2018 Notice proposed broadly excluding a circuit "having separate dedicated hardware blocks that perform separate color and texture operations," from the scope of the term "unified shader," see 83 Fed. Reg. 28660-62 (June 20, 2018), upon further analysis of the record, the Commission finds that the intrinsic evidence only supports a narrow disclaimer of "a circuit having separate dedicated hardware blocks for performing separate color shading and texture coordinate shading." Accord Complainants' Suppl. Br. at 4 ("Based on the intrinsic evidence, there are only two very specific color and texture operations that must be implemented as a shared hardware block within the unified shader, and which cannot be implemented in 'separate dedicated hardware blocks' – 'color shading' and 'texture coordinate shading.'") (citing JX-1, '506 patent at 6:43-53); IA's Suppl. Resp. at 5.

[1e] wherein each of said parallel pipelines further comprises a unified shader that is programmable to perform both color shading and texture shading.

As explained below, the Commission's modified construction for the term "unified shader" does not impact the FID's infringement analysis, particularly with respect to disputed claim element [1e] of the '506 patent which recites that term. *Accord* IA's Suppl. Br. at 12-13; Complainants' Suppl. Br. at 14-15. In particular, the unified shader of the accused Multipipe GPUs does not have separate dedicated hardware blocks that perform separate color shading and texture coordinate shading. *See*, *e.g.*, FID at 53, 59 ([

]). Accordingly, the Commission has determined to affirm the FID's infringement findings.

The evidentiary record supports by a preponderance of the evidence the FID's conclusion that the accused Multipipe GPUs satisfy the "unified shader" limitation. The FID finds that "[e]vidence submitted in this Investigation demonstrates that each of the . . . Accused Multipipe Products contains parallel pipelines further comprising a unified shader that is programmable to perform both color shading and texture shading." *See* FID at 52 (citing Hearing Tr. at 258:11-265: 14 (Reinman)); CDX-6C). The FID reasons that "[

]." See id. at 53 (citing Hearing Tr. at 260:20-261:21 (Reinman)); CDX-6C); see also id. at 53, 59 (finding that [

]).

Respondents argue that the FID "fail[s] to make a finding that any of the Accused Multipipe Products meet the claim limitation requiring 'texture shading' (as that term was construed by the ALJ)." See Respondents' Pet. at 27-28. Respondents acknowledge that the FID "addressed . . . whether the Accused Multipipe Products were capable of 'texture coordinate shading," but Respondents argue that "making a finding that the Accused Multipipe Products perform 'texture coordinate shading' does not satisfy the requirement that those products also perform 'texture shading." See id. at 26. The record does not support this contention. Both Complainants' and Respondents' experts agree that "texture coordinate shading is a subset of texture shading." See Hearing Tr. at 444:11-20 (Reinman); see also id. at 1169:12-18 (Edwards) ("[C]olor shading and texture coordinate shading . . . are types of color and texture operations, respectively."); accord Complainants' Pet. Resp. at 33-34. Thus, because the FID finds that the alleged unified shader in the accused Multipipe products performs "texture coordinate shading," the FID also finds that the alleged unified shader performs "texture shading." See FID at 58-62; accord IA's Pet. Resp. at 23.

Respondents also fault the FID and AMD for selecting a subset of functional units [

] of the Utgard GPU. See Respondents' Pet. at 28-30; accord Respondents'