# In the Matter of

# CERTAIN MEMORY MODULES AND COMPONENTS THEREOF, AND PRODUCTS CONTAINING SAME

Investigation No. 337-TA-1023

**Publication 4935**

September 2019

Washington, DC 20436

# U.S. International Trade Commission

#### **COMMISSIONERS**

Rhonda Schmidtlein, Chairman David Johanson, Vice Chairman Irving Williamson, Commissioner Meredith Broadbent, Commissioner

Address all communications to Secretary to the Commission United States International Trade Commission Washington, DC 20436

# **U.S. International Trade Commission**

Washington, DC 20436 www.usitc.gov

# In the Matter of

# CERTAIN MEMORY MODULES AND COMPONENTS THEREOF, AND PRODUCTS CONTAINING SAME

Investigation No. 337-TA-1023

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN MEMORY MODULES AND COMPONENTS THEROF, AND PRODUCTS CONTAINING SAME

Investigation No. 337-TA-1023

NOTICE OF A COMMISSION DETERMINATION TO REVIEW-IN-PART AN INITIAL DETERMINATION FINDING NO VIOLATION OF SECTION 337; ON REVIEW, TO TAKE NO POSITION ON ONE ISSUE; AFFIRMANCE OF THE FINDING OF NO VIOLATION AND TERMINATION OF THE INVESTIGATION

**AGENCY**: U.S. International Trade Commission.

**ACTION**: Notice.

**SUMMARY**: Notice is hereby given that the U.S. International Trade Commission has determined to review-in-part a final initial determination ("ID") of the presiding administrative law judge ("ALJ") finding no violation of section 337. On review, the Commission has determined to take no position on the issue under review. The Commission has also determined to affirm the ID's finding of no violation of section 337 and has terminated the investigation.

FOR FURTHER INFORMATION CONTACT: Clint Gerdine, Esq., Office of the General Counsel, U.S. International Trade Commission, 500 E Street, SW., Washington, D.C. 20436, telephone (202) 708-2310. Copies of non-confidential documents filed in connection with this investigation are or will be available for inspection during official business hours (8:45 a.m. to 5:15 p.m.) in the Office of the Secretary, U.S. International Trade Commission, 500 E Street, SW., Washington, D.C. 20436, telephone (202) 205-2000. General information concerning the Commission may also be obtained by accessing its Internet server at <a href="https://www.usitc.gov">https://www.usitc.gov</a>. The public record for this investigation may be viewed on the Commission's electronic docket (EDIS) at <a href="https://edis.usitc.gov">https://edis.usitc.gov</a>. Hearing-impaired persons are advised that information on this matter can be obtained by contacting the Commission's TDD terminal on (202) 205-1810.

SUPPLEMENTARY INFORMATION: The Commission instituted this investigation on October 7, 2016, based on a complaint filed on behalf of Netlist, Inc. of Irvine, California. 81 FR 69853-54. The complaint, as supplemented, alleged violations of section 337 of the Tariff Act of 1930, as amended, 19 U.S.C. 1337, by reason of infringement of certain claims of the following U.S. Patent Nos.: 8,756,364 ("the '364 patent"); 8,689,064; 8,516,185; 8,001,434 ("the '434 patent"); 8,359,501 ("the '501 patent"); and 8,489,837. The Commission's notice of investigation named SK Hynix Inc. of Gyeoonggi-do, Republic of Korea; and SK Hynix America

Inc. and SK Hynix Memory Solutions Inc., both of San Jose, California, as respondents. The Office of Unfair Import Investigations ("OUII") is also a party to the investigation. *Id.*

On May 31, 2017, the Commission issued notice of its determination not to review the ALJ's ID (Order No. 21) terminating the investigation as to the '364 patent based on partial withdrawal of the complaint.

On November 14, 2017, the ALJ issued his final ID and recommended determination (RD) on remedy and bonding in one document. The ID finds, *inter alia*, that none of respondents' accused products infringe any of the remaining asserted patents. The ID also finds that claims 1-3 and 5-7 of the '434 patent and claim 1 of the '501 patent are not invalid as anticipated in view of U.S. Patent Publication No. 2005/0257109 A1 ("Averbuj").

On November 27, 2017, complainant and respondents petitioned for review of the final ID. On December 5, 2017, complainant, respondents, and OUII each filed a response in opposition to the opposing petition for review. On December 5, 2017, the Chairman granted respondents' motion for leave to refile its petition for review out of time.

Having examined the record of this investigation, including the ID, the parties' petitions for review, and the responses thereto, the Commission has determined to review-in-part the final ID. Specifically, the Commission has determined to review the ID's finding that claims 1-3 and 5-7 of the '434 patent and claim 1 of the '501 patent are not anticipated by Averbuj. The Commission has determined not to review the remainder of the final ID.

On review, the Commission determines to take no position on the ID's finding that claims 1-3 and 5-7 of the '434 patent and claim 1 of the '501 patent are not invalid as anticipated in view of Averbuj. *See Beloit Corp. v. Valmet Oy*, 742 F.2d 1421 (Fed. Cir. 1984). The Commission therefore affirms the ID's finding of no violation of section 337 and terminates the investigation.

The authority for the Commission's determination is contained in section 337 of the Tariff Act of 1930, as amended, 19 U.S.C. 1337, and in part 210 of the Commission's Rules of Practice and Procedure, 19 CFR part 210.

By order of the Commission.

Lisa R. Barton

Secretary to the Commission

Issued: January 16, 2018

#### PUBLIC CERTIFICATE OF SERVICE

I, Lisa R. Barton, hereby certify that the attached NOTICE has been served by hand upon the Commission Investigative Attorney, Vu Bui, Esq., and the following parties as indicated, on January 16, 2018.

Lisa R. Barton, Secretary U.S. International Trade Commission 500 E Street, SW, Room 112 Washington, DC 20436 On Behalf of Complainant Netlist, Inc.: James M. Wodarski, Esq. ☐ Via Hand Delivery MINTZ, LEVIN, COHN, FERRIS, GLOVSKY & POPEO ☐ Via Express Delivery One Financial Center ☑ Via First Class Mail Boston, MA 02111 ☐ Other: On Behalf of Respondents SK hynix Inc., SK hynix America Inc., and SK hynix memory solutions Inc.: Michael R. Franzinger, Esq. ☐ Via Hand Delivery SIDLEY AUSTIN LLP ☐ Via Express Delivery 1501 K Street NW Washington, DC 20005 ☐ Other:

#### UNITED STATES INTERNATIONAL TRADE COMMISSION

Washington, D.C.

In the Matter of

CERTAIN MEMORY MODULES AND COMPONENTS THEREOF, AND PRODUCTS CONTAINING SAME

INV. NO. 337-TA-1023

# INITIAL DETERMINATION ON VIOLATION OF SECTION 337 AND RECOMMENDED DETERMINATION ON REMEDY AND BOND

Chief Administrative Law Judge Charles E. Bullock

(November 14, 2017)

#### **Appearances:**

For the Complainants Netlist, Inc.:

James M. Wodarski, Esq., Michael T. Renaud, Esq., Andrew H. DeVoogd, Esq., Michael J. McNamara, Esq., Michael C. Newman, Esq., Kristina R. Cary, Esq., Matthew S. Galica, Esq., Robert J. L. Moore, Esq., Daniel B. Weinger, Esq., of Mintz, Levin, Cohn, Ferris, Glovsky and Popeo PC of Boston, MA.

Aarti Shah, Esq., Andy Yu, Esq. of Mintz, Levin, Cohn, Ferris, Glovsky and Popeo PC of Washington, DC.

For the Respondents SK hynix Inc., SK hynix America Inc. and SK hynix memory solutions Inc.:

Brian R. Nester, Esq., Michael R. Franzinger, Esq., Wonjoo Suh, Esq. of Sidley Austin LLP of Washington, DC.

David T. Pritikin, Esq., Richard A. Cederoth, Esq., David C. Giardina, Esq. of Sidley Austin LLP of Chicago, IL.

Steven S. Baik, Esq., Ryuk Park, Esq., Jinyung Lee, Esq. of Sidely Austin LLP of Palo Alto, CA.

Theodore W. Chandler, Esq. of Sidely Austin LLP of Los Angeles, CA.

Michael D. Hatcher, Esq. of Sidely Austin LLP of Dallas, TX.

# For the Commission Investigative Staff:

Margaret D. Macdonald, Esq., Director; David O. Lloyd, Esq., Supervisory Attorney; Vu Q. Bui, Esq., Investigative Attorney of the Office of Unfair Import Investigations, U.S. International Trade Commission, of Washington, D.C.

# TABLE OF CONTENTS

| I.  | INT                        | RODUCTION                                                                            |                          |

|-----|----------------------------|--------------------------------------------------------------------------------------|--------------------------|

|     | A.<br>B.                   | Procedural History  The Parties                                                      | . 3                      |

|     | 1.<br>2.                   | ComplainantRespondents                                                               | . 3                      |

|     | C.<br>D.                   | Overview of the Technology  Asserted Patents                                         | . 5                      |

|     | 1.<br>2.<br>3.<br>4.<br>5. | U.S. Patent No. 8,001,434 (the "'434 patent")                                        | . 5<br>. 6<br>. 6<br>. 7 |

| II. | Juri                       | isdiction & Importation                                                              |                          |

|     | A.<br>B.<br>C.<br>D.       | Subject Matter Jurisdiction  Personal Jurisdiction  In Rem Jurisdiction  Importation | . 8<br>. 8<br>. 8        |

|     | E.                         | Standing                                                                             |                          |

| III | . R                        | Relevant Law                                                                         |                          |

|     | A.<br>B.                   | Claim Construction                                                                   | 12                       |

|     | 1.                         | Literal Infringement                                                                 | 12                       |

|     | C.                         | Validity                                                                             |                          |

|     | 1.<br>2.<br>3.<br>4.       | Anticipation (35 U.S.C. §102)                                                        | 13<br>14<br>15           |

|     | D.                         | Domestic Industry                                                                    |                          |

|     | 1.<br>2.                   | Economic Prong Technical Prong                                                       | 17                       |

| IV  | 7. τ                       | J.S. PATENT NO. 8,001,434                                                            |                          |

|     | A.                         | Overview                                                                             |                          |

|     | 1.                         | Asserted Claims                                                                      |                          |

|     | B.<br>C.                   | Level of Ordinary Skill in the Art                                                   | 20                       |

|     | 1.                         | "self-testing memory module"                                                         | 20                       |

| 2. "generate"                     |                                                  | 23 |

|-----------------------------------|--------------------------------------------------|----|

| 3. "Test"                         |                                                  | 30 |

| 4. "wherein the c                 | ircuit is configured to test the memory devices" | 33 |

| D. Infringement                   |                                                  | 34 |

|                                   |                                                  |    |

| <ol> <li>Asserted Depe</li> </ol> | endent Claims 2, 3 and 5-7                       | 42 |

| E. Domestic Industr               | ry – Technical Prong                             | 42 |

| F. Validity                       |                                                  | 44 |

| 1. Expert Testime                 | ony of Mr. Hoffman                               | 44 |

| 2. Anticipation                   |                                                  | 46 |

|                                   |                                                  |    |

| V. U.S. PATENT NO. 8              | 3,359,501                                        | 59 |

| A. Overview                       |                                                  | 59 |

| 1. Asserted Clair                 | ns                                               | 59 |

| B. Level of Ordinar               | ry Skill in the Art                              | 60 |

| C. Claim Construct                | ion                                              | 60 |

| D. Infringement                   |                                                  | 61 |

|                                   |                                                  |    |

| *                                 | aim 4                                            |    |

| E. Domestic Indust                | ry – Technical Prong                             | 62 |

|                                   |                                                  |    |

| 1. Anticipation                   |                                                  | 63 |

|                                   |                                                  |    |

|                                   | 0. 8,689,064                                     |    |

|                                   |                                                  |    |

| 1. Asserted Clair                 | ms                                               | 71 |

| B. Level of Ordinar               | ry Skill in the Art                              | 71 |

| C. Claim Construct                | tion                                             | 72 |

| <del>-</del>                      |                                                  |    |

|                                   |                                                  |    |

| E. Domestic Indust                | try – Technical Prong                            | 73 |

| F. Validity                       |                                                  | 75 |

| 1. Anticipation                   |                                                  | 75 |

| 2. Indefiniteness                 |                                                  | 78 |

| VII. U.S. PATENT NO               | 0. 8,489,837                                     | 79 |

| A. Overview                       |                                                  | 79 |

| 1. Asserted Clair                 | ms                                               |    |

| B. Level of Ordina                | ry Skill in the Art                              | 80 |

| C.                   | Claim Construction                                                                                                                                 |            |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.<br>2.             | "notification signal""execute an interrupt routine"                                                                                                | 82<br>85   |

| D.                   | Infringement                                                                                                                                       | 89         |

| 1.<br>2.             | Independent Claim 1  Dependent Claims 2, 3, 5 and 6                                                                                                | 89<br>99   |

| E.<br>F. V           | Domestic Industry – Technical Prong                                                                                                                | 100        |

| 1.<br>2.             | Anticipation Obviousness                                                                                                                           | 111        |

| VIII.                | U.S. PATENT NO. 8,516,185                                                                                                                          | 112        |

| A.                   | Overview                                                                                                                                           | 112        |

| 1.                   | Asserted Claims                                                                                                                                    |            |

| B.<br>C.<br>D.       | Level of Ordinary Skill in the Art  Claim Construction  Infringement                                                                               | 116        |

| 1.<br>2.             | Independent Claim 1  Dependent Claims 2, 3, 5 and 6                                                                                                |            |

| E.<br>F. V           | Domestic Industry – Technical ProngValidity                                                                                                        | 131        |

| 1.<br>2.<br>3.       | Anticipation                                                                                                                                       | 134        |

| IX. I                | Domestic Industry – Economic Prong                                                                                                                 | 153        |

| A.                   | Netlist HyperCloud Products                                                                                                                        | 153        |

| 1.<br>2.<br>3.       | 337(a)(3)(A) - Significant Investment in Plant and Equipment                                                                                       | 158        |

| B.                   | Netlist HybriDIMM Products                                                                                                                         | 164        |

| X. Co                | onclusions of Law                                                                                                                                  | 165        |

|                      | Recommended Determiantion on Remedy & Bond                                                                                                         |            |

| A.<br>B.<br>C.       | Limited Exclusion Order  Cease and Desist Order  Bond During Presidential Review                                                                   | 169        |

| XII. I               | Public Interest                                                                                                                                    | 172        |

| A.<br>B.<br>C.<br>D. | Public Health and Welfare  Competitive Conditions in the U.S. Economy  Production of Like or Directly Competitive Products in U.S.  U.S. Consumers | 175<br>178 |

| . ·                  | UINI UUMAAAN IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                                                                                                    |            |

| E     | RAND Obligations      | 181 |

|-------|-----------------------|-----|

| XIII. | Initial Determination | 197 |

## TABLE OF ABBREVIATIONS

| CDX  | Complainant's demonstrative exhibit      |

|------|------------------------------------------|

| CIB  | Complainant's initial post-hearing brief |

| СРВ  | Complainant's pre-hearing brief          |

| CPX  | Complainant's physical exhibit           |

| CRB  | Complainant's reply post-hearing brief   |

| CX   | Complainant's exhibit                    |

| Dep. | Deposition                               |

| JX   | Joint Exhibit                            |

| RDX  | Respondent's demonstrative exhibit       |

| RIB  | Respondent's initial post-hearing brief  |

| RPX  | Respondent's physical exhibit            |

| RPB  | Respondent's Pre-hearing brief           |

| RRB  | Respondent's reply post-hearing brief    |

| RRX  | Respondent's rebuttal exhibit            |

| RX   | Respondent's exhibit                     |

| SIB  | Staff's initial post-hearing brief       |

| SRB  | Staff's reply post-hearing brief         |

| Tr.  | Transcript                               |

## UNITED STATES INTERNATIONAL TRADE COMMISSION

Washington, D.C.

In the Matter of

CERTAIN MEMORY MODULES AND COMPONENTS THEREOF, AND PRODUCTS CONTAINING SAME

INV. NO. 337-TA-1023

# INITIAL DETERMINATION ON VIOLATION OF SECTION 337 AND RECOMMENDED DETERMINATION ON REMEDY AND BOND

Chief Administrative Law Judge Charles E. Bullock

(November 14, 2017)

Pursuant to the Notice of Investigation, 81 Fed. Reg. 69853 (Oct. 7, 2016), this is the Initial Determination in the matter of Certain Memory Modules and Components thereof, and Products Containing Same, Investigation No. 337-TA-1023.

For the reasons stated herein, the undersigned has determined that no violation of section 337 of the Tariff Act of 1930, as amended, has occurred in the importation into the United States, the sale for importation, or the sale within the United States after importation of certain memory modules and components thereof, and products containing same with respect to U.S. Patents Nos. 8,001,434; 8,359,501; 8,689,064; 8,489,837; and 8,516,185.

#### I. INTRODUCTION

#### A. Procedural History

On September 1, 2016, Complainant Netlist, Inc. ("Netlist" or "Complainant") filed a Complaint alleging violations of section 337 based upon the sale for importation, importation, or sale within the United States after importation of certain memory modules and components thereof, and products containing same. *See* 81 *Fed. Reg.* 69853 (Oct. 7, 2016). On September 22 and 23, 2016, Netlist supplemented the complaint. *Id.*

On October 7, 2016, the Commission instituted this Investigation to determine:

whether there is a violation of subsection (a)(1)(B) of section 337 in the importation into the United States, the sale for importation, or the sale within the United States after importation of certain memory modules and components thereof, and products containing same by reason of infringement of one or more of claims 1-4, 6, 7, 10, 13, 17, and 23 of the '364 patent'; claims 1-3, 7, 8, and 10-12 of the '185 patent; claims 2,3 and 5-7 of the '434 patent; claim 4 of the '501 patent; claim 16 of the '064 patent; and claims 1-3, 5, and 6 of the '837 patent, and whether an industry in the United States exists or is in the process of being established as required by subsection (a)(2) of section 337;

Id. at 69853-54.

The named respondents are SK Hynix Inc. of Gyeoonggi-do, Republic of Korea; SK Hynix America, Inc. of San Jose, California; and SK Hynix memory solutions Inc. of San Jose, California (collectively, "SK hynix" or "Respondents"). (*Id.* at 69854.) The Commission Investigative Staff ("Staff") is also a party to this Investigation. (*Id.*)

The evidentiary hearing was held May 8-11, 2017.

On May 4, 2017, Netlist moved for partial termination of the investigation with respect to the '364 patent. (Mot. No. 1023-032.) The presiding ALJ at that time issued an Initial Determination granting that motion and terminating the investigation with respect to the '364 patent. Order No. 21 (May 5, 2017); see also Notice of Comm'n. Determination Not to Review an Initial Determination Terminating-in-Part the Investigation Based on Partial Withdrawal of the Compl. (May 31, 2017).

#### B. The Parties

# 1. Complainant

Complainant Netlist, Inc. is a Delaware corporation with a principal place of business at 175 Technology Drive, Suite 150, Irvine, California. (Complaint at ¶7; CX-0001C at Q/A 49.) Netlist is in the business of designing, developing, manufacturing, and supporting high-performance memory modules. (CX-0001C at Q/A 51, 55.)

### 2. Respondents

#### a) SK hynix Inc.

SK hynix Inc. is a Korean corporation, having a principal place of business at 2091, Gyeonghung-daero, Bubal-eub, Icheon-si, Gyeonggi-do, Korea. (Resp. to Complaint at ¶30.) SK hynix Inc. is the parent corporation of Respondents SK hynix America Inc. and SK hynix memory solutions Inc. (*Id.*) SK hynix Inc. is a manufacturer and supplier of dynamic random-access memory ("DRAM") chips and memory modules, including the accused DDR4 LRDIMM and RDIMM products in this investigation. (*See* RX-0002C at Q/A 7.)

# b) SK hynix America Inc.

Respondent SK hynix America Inc. is a California corporation, having a principal place of business at 3101 North 1<sup>st</sup> Street, San Jose, California. (Resp. to Complaint at ¶31.) SK hynix America provides sales and technical support, and assists with customer relationships in the United States for SK hynix Inc. (*Id.*; RX-0001C at Q/A 45.)

## c) SK hynix memory solutions Inc.

SK hynix memory solutions Inc. is a Delaware corporation, having a principal place of business at 3103 North 1<sup>st</sup> Street, San Jose, California. (Resp. to Complaint at ¶32.) SK hynix memory solutions Inc. is a wholly-owned subsidiary of SK hynix Inc. that performs research and

development and provides customers with controller hardware and flash management systems and firmware for devices. (*Id.*; RX-0001C at Q/A 50.)

#### C. Overview of the Technology

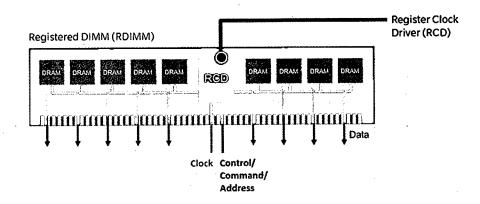

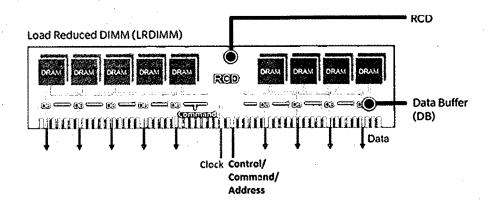

The technology in this investigation relates to two types of memory modules: DDR4 Registered Dual In-Line Memory Modules ("RDIMMs") and DDR4 Load-Reduced Dual In-Line Memory Modules ("LRDIMMs"). (Complaint at ¶35.) Both RDIMMs and LRDIMMs are designed for use in servers to store data that must be readily available for certain software applications, and to allow quick and efficient retrieval of that data. (RX-0004C at Q/A 204.) The DDR4 designation refers to the particular generation of the DRAM chips on the memory module. DDR4 is the most recent generation of these DRAM chips, preceded by DDR3, then DDR2, etc. (Id. at Q/A 201.)

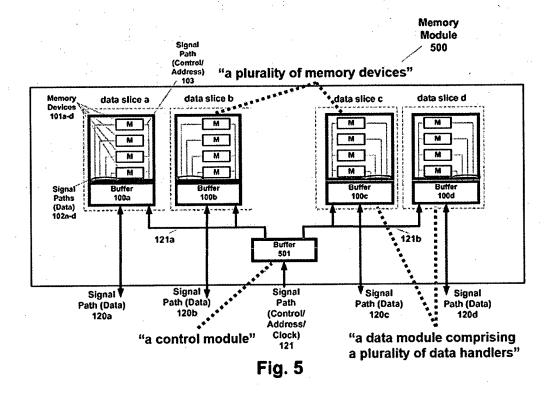

RDIMMs and LRDIMMS share several similar components, including a printed circuit board, DRAM chips, and a Register/ing Clock Driver ("RCD"). (See CX-0840 at 3; CX-0005C at Q/A 69, 71.) LRDIMMS also contain Data Buffers ("DBs") on the printed circuit board. (See CX-0840 at 3; CX-0005C at Q/A 71.) Complainants provide the following diagrammatic examples of an RDIMM and a LRDIMM, respectively:

(CIB at 12-14.)

#### D. Asserted Patents

## 1. U.S. Patent No. 8,001,434 (the "'434 patent")

The '434 patent is titled "Memory Board with Self-Testing Capability." (JX-0003 ('434 Patent) at Cover.) It issued August 16, 2011 from a patent application filed April 13, 2009. (*Id.*) The patent lists Hyun Lee of Ladera Ranch, CA, Jayesh R. Bhakta of Cerritos, CA, and Soonju Choi of Irvine, CA as the inventors. (*Id.*) Netlist, Inc. of Irvine, CA is listed as the assignee. (*Id.*) The '434 patent generally relates to self-testing memory modules. (*See id.* at Abstract.) Complainant asserts claims 2, 3, and 5-7 in this investigation.

The '434 patent is one of three asserted patents that share a common specification. The parties refer to these three patents collectively as the "Self-Test Patents." (See SIB at 11, n.3.)

# 2. U.S. Patent No. 8,359,501 (the "'501 patent")

The '501 patent is also titled "Memory Board with Self-Testing Capability." (JX-0004 ('501 Patent) at Cover.) It issued January 22, 2013 from a patent application filed July 14, 2011. (Id.) The patent lists Hyun Lee of Ladera Ranch, CA, Jayesh R. Bhakta of Cerritos, CA and Sooniu Choi of Irvine, CA as the inventors. (Id.) Netlist, Inc. of Irvine, CA is listed as the

assignee. (*Id.*) Like the '434 patent, the '501 patent generally relates to self-testing memory modules. (*See id.* at Abstract.) Complainant asserts claim 4 of the '501 patent in this investigation.

The '501 patent is the second of the "self-test patents" and it issued from a continuation application of the '434 patent, and shares a common specification with the '434 patent. (*See id.* at Cover.)

# 3. U.S. Patent No. 8,689,064 (the "'064 patent")

The '064 patent is titled "Apparatus and Method for Self-Test in a Multi-Rank Memory Module." (JX-0005 ('064 Patent) at Cover.) It issued on April 1, 2014 from a patent application filed January 19, 2013. (*Id.*) The patent lists Hyun Lee of Ladera Ranch, CA, Jayesh R. Bhakta of Cerritos, CA, and Soonju Choi of Irvine, CA as the inventors. (*Id.*) Netlist, Inc. of Irvine, CA is listed as the assignee. (*Id.*) Like the '434 and '501 patents, the '064 patent generally relates to self-testing memory modules. (*See id.* at Abstract.) Complainant asserts claim 16 of the '064 patent in this investigation.

The '064 patent is the third of the "self-test patents." The '064 patent issued from a continuation application of the '501 patent, and shares a common specification with the '501 and '434 patents. (See id. at Cover.)

# 4. U.S. Patent No. 8,489,837 (the "'837 patent")

The '837 patent is titled "Systems and Methods for Handshaking with a Memory Module." (JX-0006 ('837 Patent)<sup>2</sup> at Cover.) It issued on July 16, 2013 from a patent application filed June 14, 2010. (*Id.*) The patent lists Hyun Lee of Ladera Ranch, CA as the inventor. (*Id.*) Netlist, Inc. of Irvine, CA is listed as the assignee. (*Id.*) The '837 patent generally relates to memory modules

Staff indicates that the '837 patent has also been referred to as the "Handshake Patent" in this investigation. (SIB at 13, n.5.)

that perform handshaking during or upon completion of initialization. (*Id.* at 1:15-17.) Complainant asserts claims 1-3, 5 and 6 of the '837 patent in this investigation.

# 5. U.S. Patent No. 8,516,185 (the "'185 patent")

The '185 patent is titled "System and Method Utilizing Distributed Byte-Wise Buffers on a Memory Module." (JX-0002 ('185 Patent)<sup>3</sup> at Cover.) It issued on August 20, 2013 from a patent application filed April 15, 2010. (*Id.*) The patent lists Hyun Lee of Ladera Ranch, CA and Jayesh R. Bhakta of Cerritos, CA as the inventors. (*Id.*) Netlist, Inc. of Irvine, CA is listed as the assignee. (*Id.*) The '185 patent generally relates to "memory subsystems of computer systems, and more specifically to systems, devices, and methods for improving the performance and the memory capacity of memory subsystems or memory 'boards,' particularly memory boards that include dual inline memory modules (DIMMs)." (*Id.* at 1:13-19.) Complainant asserts claims 1-3, 7, 8 and 10-12 of the '185 patent in this investigation.

#### II. JURISDICTION & IMPORTATION

# A. Subject Matter Jurisdiction

Section 337 confers subject matter jurisdiction on the Commission to investigate, and if appropriate, to provide a remedy for, unfair acts and unfair methods of competition in the importation, the sale for importation, or the sale after importation of articles into the United States. See 19 U.S.C. §§ 1337(a)(1)(B) and (a)(2). Netlist filed a complaint alleging a violation of this subsection. Accordingly, the Commission has subject matter jurisdiction over this Investigation under section 337 of the Tariff Act of 1930. See Amgen, Inc. v. U.S. Int'l. Trade Comm'n., 902 F.2d 1532, 1536 (Fed. Cir. 1990).

Staff indicates that the '185 patent has also been referred to as the "Load Reduction Patent" in this investigation. (SIB at 15 n.6.)

#### B. Personal Jurisdiction

Respondents have appeared and participated in this Investigation. The Commission therefore has personal jurisdiction over Respondents. *See, e.g., Certain Optical Disk Controller Chips & Chipsets & Prods. Containing Same, Including DVD Players & PC Optical Storage Devices*, Inv. No. 337-TA-506, Initial Determination at 4-5 (May 16, 2005) (unreviewed in relevant part).

#### C. In Rem Jurisdiction

Respondents do not dispute that the Commission has *in rem* jurisdiction over the SK hynix accused products that have been imported into the United States. (RIB at 6.) In fact, Respondents admit that "SK hynix America Inc. imports the accused DDR4 LRDIMM and RDIMM memory modules into the United States." (*Id.*) Accordingly, the Commission has *in rem* jurisdiction over the accused products.

# D. Importation

As noted above, Respondents do not dispute that they import the accused RDIMM and LRDIMM memory modules. (*See* RIB at 6; Respondents' Answer at Conf. Ex. A; CX-0218C at RFA No. 472-653.) Accordingly, the importation requirement of section 337 is satisfied.

#### E. Standing

Netlist asserts that it has standing to bring this investigation based on its rights and interest in the asserted patents. (CIB at 19 (citing JX-0013; JX-0014; JX-0015; JX-0016; JX-0017; JX-0018).) However, SK hynix argues that Netlist lacks standing because it has not satisfied the domestic industry requirement of section 337. (RIB at 6.) Staff submits that the assignment records for the asserted patents (*i.e.*, JX-0013; JX-0014; JX-0015; JX-0016; JX-0017; JX-0018) demonstrate that Netlist has standing, and argues that Respondents have improperly conflated standing with the domestic industry requirement. (SIB at 28.)

SK hynix offers no precedent supporting its interpretation of the domestic industry requirement as a question of standing. Indeed, other than a single sentence in their initial post-hearing brief, Respondents never address the issue of standing again. (*Cf.* RIB at 6.) As Staff and Netlist both noted, the evidence of record shows that Netlist holds all of the rights and interests in the asserted patents in this investigation. (*See* JX-0013; JX-0014; JX-0015; JX-0016; JX-0017; JX-0018.) This showing is sufficient to establish Netlist's standing to bring this suit. Respondents have not presented argument or evidence that overcomes that showing. Accordingly, the undersigned finds that Netlist has standing in this investigation.

#### III. RELEVANT LAW

#### A. Claim Construction

"An infringement analysis entails two steps. The first step is determining the meaning and scope of the patent claims asserted to be infringed. The second step is comparing the properly construed claims to the device accused of infringing." *Markman v. Westview Instruments, Inc.*, 52 F.3d 967, 976 (Fed. Cir. 1995) (en banc) (internal citations omitted), *aff'd*, 517 U.S. 370 (1996). Claim construction is a "matter of law exclusively for the court." *Id.* at 970-71. "The construction of claims is simply a way of elaborating the normally terse claim language in order to understand and explain, but not to change, the scope of the claims." *Embrex, Inc. v. Serv. Eng 'g Corp*, 216 F.3d 1343, 1347 (Fed. Cir. 2000).

Claim construction focuses on the intrinsic evidence, which consists of the claims themselves, the specification, and the prosecution history. See Phillips v. AWH Corp, 415 F.3d 1303, 1314 (Fed. Cir. 2005) (en banc); see also Markman, 52 F.3d at 979. As the United States Court of Appeals for the Federal Circuit ("Federal Circuit") explained in Phillips, courts must analyze each of these components to determine the "ordinary and customary meaning of a claim

term" as understood by a person of ordinary skill in the art at the time of the invention. 415 F.3d at 1313. "Such intrinsic evidence is the most significant source of the legally operative meaning of disputed claim language." *Bell Atl. Network Servs., Inc. v. Covad Commc'ns Grp., Inc.*, 262 F.3d 1258, 1267 (Fed. Cir. 2001).

"It is a 'bedrock principle' of patent law that 'the claims of a patent define the invention to which the patentee is entitled the right to exclude." *Phillips*, 415 F.3d at 1312 (quoting *Innova/Pure Water, Inc. v. Safari Water Filtration Sys., Inc.*, 381 F.3d 1111, 1115 (Fed. Cir. 2004)). "Quite apart from the written description and the prosecution history, the claims themselves provide substantial guidance as to the meaning of particular claims terms." *Id.* at 1314; *see also Interactive Gift Express, Inc. v. Compuserve Inc.*, 256 F.3d 1323, 1331 (Fed. Cir. 2001) ("In construing claims, the analytical focus must begin and remain centered on the language of the claims themselves, for it is that language that the patentee chose to use to 'particularly point[] out and distinctly claim[] the subject matter which the patentee regards as his invention.""). The context in which a term is used in an asserted claim can be "highly instructive." *Phillips*, 415 F.3d at 1314. Additionally, other claims in the same patent, asserted or unasserted, may also provide guidance as to the meaning of a claim term. *Id.*

The specification "is always highly relevant to the claim construction analysis. Usually, it is dispositive; it is the single best guide to the meaning of a disputed term." *Id.* at 1315 (quoting *Vitronics Corp. v. Conceptronic, Inc.*, 90 F.3d 1576, 1582 (Fed. Cir. 1996)). "[T]he specification may reveal a special definition given to a claim term by the patentee that differs from the meaning it would otherwise possess. In such cases, the inventor's lexicography governs." *Id.* at 1316. "In other cases, the specification may reveal an intentional disclaimer, or disavowal, of claim scope by the inventor." *Id.* As a general rule, however, the particular examples or embodiments discussed

in the specification are not to be read into the claims as limitations. *Id.* at 1323. In the end, "[t]he construction that stays true to the claim language and most naturally aligns with the patent's description of the invention will be . . . the correct construction." *Id.* at 1316 (quoting *Renishaw PLC v. Marposs Societa' per Azioni*, 158 F.3d 1243, 1250 (Fed. Cir. 1998)).

In addition to the claims and the specification, the prosecution history should be examined, if in evidence. *Id.* at 1317; *see also Liebel-Flarsheim Co. v. Medrad Inc.*, 358 F.3d 898, 913 (Fed. Cir. 2004). The prosecution history can "often inform the meaning of the claim language by demonstrating how the inventor understood the invention and whether the inventor limited the invention in the course of prosecution, making the claim scope narrower than it would otherwise be." *Phillips*, 415 F.3d at 1317; *see also Chimie v. PPG Indus. Inc.*, 402 F.3d 1371, 1384 (Fed. Cir. 2005) ("The purpose of consulting the prosecution history in construing a claim is to 'exclude any interpretation that was disclaimed during prosecution."").

When the intrinsic evidence does not establish the meaning of a claim, then extrinsic evidence (*i.e.*, all evidence external to the patent and the prosecution history, including dictionaries, inventor testimony, expert testimony, and learned treatises) may be considered. *Phillips*, 415 F.3d at 1317. Extrinsic evidence is generally viewed as less reliable than the patent itself and its prosecution history in determining how to define claim terms. *Id.* at 1317. "The court may receive extrinsic evidence to educate itself about the invention and the relevant technology, but the court may not use extrinsic evidence to arrive at a claim construction that is clearly at odds with the construction mandated by the intrinsic evidence." *Elkay Mfg. Co. v. Ebco Mfg. Co.*, 192 F.3d 973, 977 (Fed. Cir. 1999).

If, after a review of the intrinsic and extrinsic evidence, a claim term remains ambiguous, the claim should be construed so as to maintain its validity. *Phillips*, 415 F.3d at 1327. Claims,

however, cannot be judicially rewritten in order to fulfill the axiom of preserving their validity. See Rhine v. Casio, Inc, 183 F.3d 1342, 1345 (Fed. Cir. 1999). Thus, "if the only claim construction that is consistent with the claim's language and the written description renders the claim invalid, then the axiom does not apply and the claim is simply invalid." Id.

#### B. Infringement

In a section 337 investigation, the complainant bears the burden of proving infringement of the asserted patent claims by a preponderance of the evidence. *See Spansion, Inc. v. Int'l Trade Comm'n*, 629 F.3d 1331, 1349 (Fed. Cir. 2010). This standard "requires proving that infringement was more likely than not to have occurred." *Warner-Lambert Co. v. Teva Pharm. USA, Inc.*, 418 F.3d 1326, 1341 n.15 (Fed. Cir. 2005).

#### 1. Literal Infringement

Literal infringement is a question of fact. *See Finisar Corp. v. DirecTV Grp., Inc.*, 523 F.3d 1323, 1332 (Fed. Cir. 2008). Literal infringement requires the patentee to prove that the accused device contains each limitation of the asserted claim(s). If any claim limitation is absent, there is no literal infringement of that claim as a matter of law. *See Bayer AG v. Elan Pharm. Research Corp.*, 212 F.3d 1241, 1247 (Fed. Cir. 2000).

#### C. Validity

A patent is presumed valid. 35 U.S.C. § 282; *Microsoft Corp. v. i4i Ltd. P'ship*, 131 S. Ct. 2238, 2242 (2011). A respondent who has raised patent invalidity as an affirmative defense has the burden of overcoming this presumption by clear and convincing evidence. *See Microsoft*, 131 S. Ct. at 2242. As with an infringement analysis, an analysis of invalidity involves two steps: determining the scope of the claim and comparing the properly construed claim with the prior art to determine whether the claimed invention is anticipated and/or rendered obvious.

# 1. Anticipation (35 U.S.C. § 102)

Under 35 U.S.C. § 102, a claim is anticipated and therefore invalid when "the four comers of a single, prior art document describe every element of the claimed invention, either expressly or inherently, such that a person of ordinary skill in the art could practice the invention without undue experimentation." *Advanced Display Sys., Inc. v. Kent State Univ.*, 212 F.3d 1272, 1282 (Fed. Cir. 2000), *cert. denied*, 532 U.S. 904 (2001). To be considered anticipatory, the prior art reference must be enabling and describe the applicant's claimed invention sufficiently to have placed it in possession of a person of ordinary skill in the field of the invention. *Helifix Ltd. v. Blok-Lok, Ltd.*, 208 F.3d 1339, 1346 (Fed. Cir. 2000).

#### 2. Obviousness (35 U.S.C. § 103)

Under 35 U.S.C. §103, a patent may be found invalid as obvious if "the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would have been obvious at the time the invention was made to a person having ordinary skill in the art to which said subject matter pertains." 35 U.S.C. §103(a). Because obviousness is determined at the time of invention, rather than the date of application or litigation, "[t]he great challenge of the obviousness judgment is proceeding without any hint of hindsight." *Star Scientific, Inc. v. R.J. Reynolds Tobacco Co.*, 655 F.3d 1364, 1375 (Fed. Cir. 2011) ("*Star IP*").

When a patent is challenged as obvious, the critical inquiry in determining the differences between the claimed invention and the prior art is whether there is an apparent reason to combine the known elements in the fashion claimed by the patent at issue. *See KSR Int'l Co. v. Teleflex, Inc.*, 550 U.S. 398, 417-418 (2007). The Federal Circuit has since held that when a patent is challenged as obvious, based on a combination of several prior art references, "the burden falls on the patent challenger to show by clear and convincing evidence that a person of ordinary skill in the art would

have had reason to attempt to make the composition or device, or carry out the claimed process, and would have had a reasonable expectation of success in doing so." *PharmaStem Therapeutics, Inc.* v. *ViaCell, Inc.*, 491 F.3d 1342, 1360 (Fed. Cir. 2007) (citations omitted).

Obviousness is a determination of law based on underlying determinations of fact. Star II, 655 F.3d at 1374. The factual determinations behind a finding of obviousness include: (1) the scope and content of the prior art, (2) the level and content of the prior art, (3) the differences between the claimed invention and the prior art, and (4) secondary considerations of nonobviousness. KSR, 550 U.S. at 399 (citing Graham v. John Deere Co., 383 U.S. 1, 17 (1966)). These factual determinations are referred to collectively as the "Graham factors." Secondary considerations of non-obviousness include commercial success, long felt but unresolved need, When present, secondary considerations "give light to the and the failure of others. Id. circumstances surrounding the origin of the subject matter sought to be patented," but they are not dispositive on the issue of obviousness. Geo. M. Martin Co. v. Alliance Mach. Sys. Int'l., 618 F.3d 1294, 1304-06 (Fed. Cir. 2010). A court must consider all of the evidence from the Graham factors before reaching a decision on obviousness. For evidence of secondary considerations to be given substantial weight in the obviousness determination, its proponent must establish a nexus between the evidence and the merits of the claimed invention. See W. Union Co. v. MoneyGram Payment Sys. Inc., 626 F.3d 1361, 1372-73 (Fed. Cir. 2010) (citing In re GPAC Inc., 57 F.3d 1573, 1580 (Fed. Cir. 1995)).

# 3. Written Description (35 U.S.C. § 112, (a)/¶1)

The hallmark of the written description requirement is the disclosure of the invention. *See Ariad Pharm., Inc. v. Eli Lilly and Co.*, 598 F.3d 1336, 1351 (Fed. Cir. 2010) (*en banc*). The test for determining the sufficiency of the written description in a patent requires "an objective inquiry

into the four corners of the specification from the perspective of a person of ordinary skill in the art. Based on that inquiry, the specification must describe an invention understandable to that skilled artisan and show that the inventor actually invented the invention claimed." *Id.* Compliance with the written description requirement is a question of fact and "the level of detail required to satisfy the written description requirement varies depending on the nature and scope of the claims and on the complexity and predictability of the relevant technology." *Id.*

# 4. Enablement (35 U.S.C. § 112, (a)/¶1)

To satisfy the enablement requirement a patent specification must "contain a written description of the invention . . . to enable any person skilled in the art . . . to make and use the same." 35 U.S.C. §112, ¶1. The specification must enable a person of ordinary skill in the art to practice the claimed invention without undue experimentation. *Transocean Offshore Deepwater Drilling, Inc. v. Maersk Contractors USA, Inc.*, 617 F.3d 1296, 1305 (Fed. Cir. 2010). Although a specification need not disclose minor details that are well known in the art, this is "merely a rule of supplementation, not a substitute for a basic enabling disclosure." *Auto. Tech. Int 'l Inc.*, v. BMW of N. Am., 501 F.3d 1274, 1283 (Fed. Cir. 2007) (quoting Genentech, Inc. v. Novo Nordisk, A/S, 108 F.3d 1361, 1366 (Fed. Cir. 1997)). "It is the specification, not the knowledge of one killed in the art, that must supply the novel aspects of an invention in order to constitute adequate enablement." *Auto. Tech.*, 501 F.3d at 1283.

Enablement is a question of law with underlying questions of fact regarding undue experimentation. *Transocean*, 617 F.3d at 1305. The factors weighed by a court in determining whether a disclosure requires undue experimentation include: (1) the quantity of experimentation necessary, (2) the amount of direction provided, (3) the presence of working examples, (4) the nature of the invention, (5) the state of the prior art, (6) the relative skill of those in the art, (7)

the predictability of the art, and (8) the breadth of the claims. *In re Wands*, 858 F.2d 731, 737 (Fed. Cir. 1988). Undue experimentation is "a matter of degree" and "not merely quantitative, since a considerable amount of experimentation is permissible, if it is merely routine, or if the specification in question provides a reasonable amount of guidance with respect to the direction in which the experimentation should proceed." *PPG Indus., Inc, v. Guardian Indus. Corp.*, 75 F.3d 1558, 1564 (Fed. Cir. 1996); *Northpoint Tech, Ltd. v. MDS Am, Inc.*, 413 F.3d 1301, 1318 (Fed. Cir. 2005).

# 5. Indefiniteness (35 U.S.C. § 112, (b)/¶2)

A claim must also be definite. Pursuant to 35 U.S.C. § 112(b): "The specification shall conclude with one or more claims particularly pointing out and distinctly claiming the subject matter which the inventor or joint inventor regards as the invention." 35 U.S.C. § 112(b). In *Nautilus, Inc.* v. *Biosig Instruments, Inc.*, 134 S. Ct. 2120 (2014), the Supreme Court held that § 112(b) requires "that a patent's claims, viewed in light of the specification and prosecution history inform those skilled in the art about the scope of the invention with reasonable certainty." *Id.* at 2129. A patent claim that is indefinite is invalid. 35 U.S.C. § 282(b)(3)(A).

#### D. Domestic Industry

In a patent-based complaint, a violation of section 337 can be found "only if an industry in the United States, relating to the articles protected by the patent . . . concerned, exists or is in the process of being established." 19 U.S.C. § 1337(a)(2). Under Commission precedent, this "domestic industry requirement" of section 337 consists of an economic prong and a technical prong. See Certain Stringed Musical Instruments and Components Thereof, Inv. No. 337-TA-586, Comm'n. Op. at 12-14, 2009 WL 5134139 (U.S.I.T.C. Dec. 2009). The complainant bears the burden of establishing that the domestic industry requirement is satisfied. See Certain Set-

Top Boxes and Components Thereof, Inv. No. 337-TA-454, Final Initial Determination at 294, 2002 WL 31556392 (U.S.I.T.C. June 21, 2002) (unreviewed by Commission in relevant part).

#### 1. Economic Prong

Section 337(a)(3) sets forth the following economic criteria for determining the existence of a domestic industry in such investigations:

- (3) For purposes of paragraph (2), an industry in the United States shall be considered to exist if there is in the United States, with respect to the articles protected by the patent, copyright, trademark, mask work, or design concerned

- (A) significant investment in plant and equipment;

- (B) significant employment of labor or capital; or

- (C) substantial investment in its exploitation, including engineering, research and development, or licensing.

Given that these criteria are listed in the disjunctive, satisfaction of any one of them will be sufficient to meet the economic prong of the domestic industry requirement. *See Certain Integrated Circuit Chipsets and Prods. Containing Same*, Inv. No. 337-TA-428, Order No. 10, Initial Determination (unreviewed) (May 4, 2000).

# 2. Technical Prong

The technical prong of the domestic industry requirement is satisfied when the complainant in a patent-based section 337 investigation establishes that it is practicing or exploiting the patents at issue. See 19 U.S.C. § 1337(a)(2) and (3); Certain Microsphere Adhesives, Process for Making Same and Prods. Containing Same, Including Self-Stick Repositionable Notes, Inv. No. 337-TA-366, Comm'n Op. at 8, 1996 WL 1056095 (U.S.I.T.C. Jan. 16, 1996). "The test for satisfying the 'technical prong' of the industry requirement is essentially [the] same as that for infringement, i.e., a comparison of domestic products to the asserted claims." Alloc, Inc. v. Int'l Trade Comm'n, 342 F.3d 1361, 1375 (Fed. Cir. 2003). To prevail, the patentee must establish by a preponderance of

the evidence that the domestic product practices one or more claims of the patent, either literally or under the doctrine of equivalents. *See Bayer*, 212 F.3d at 1247. It is sufficient to show that the products practice any claim of that patent, not necessarily an asserted claim of that patent. *See Certain Microsphere Adhesives*, Comm'n Op. at 7-16.

#### IV. U.S. PATENT NO. 8,001,434

#### A. Overview

#### 1. Asserted Claims

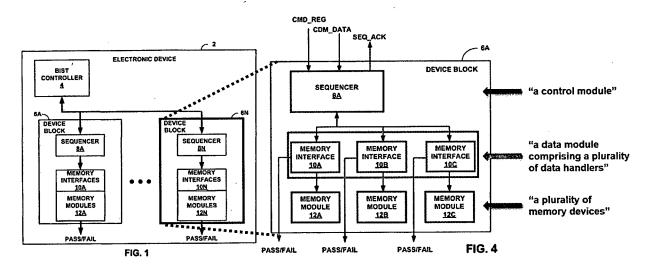

Complainants assert claims 2, 3 and 5-7 of the '434 patent. Each of the asserted claims depends from independent claim 1. Those claims provide as follows:

# 1. A self-testing memory module, comprising:

a printed circuit board configured to be operatively coupled to a memory controller of a computer system;

a plurality of memory devices on the printed circuit board, each memory device of the plurality of memory devices comprising data, address, and control ports; and

a circuit comprising:

a control module configured to generate address and control signals for testing the memory devices; and

a data module comprising a plurality of data handlers, each data handler operable independently from each of the other data handlers of the plurality of data handlers and operatively coupled to a corresponding plurality of the data ports of one or more of the memory devices and configured to generate data for writing to the corresponding plurality of data ports, wherein the circuit is configured to test the memory devices using the address and control signals generated by the control module and the data generated by the plurality of data handlers.

\* \* \* \* \*

2. The self-testing memory module of claim 1, wherein the plurality of data handlers comprise at least two physically separate components mounted on the printed circuit board.

\* \* \* \* \*

3. The self-testing memory module of claim 2, wherein the plurality of data handlers comprise at least two physically separate integrated circuit packages.

\* \* \* \* \*

5. The self-testing memory module of claim 2, wherein each of the plurality of data handlers is positioned on the printed circuit board proximate to the corresponding plurality of data ports.

\* \* \* \* \*

6. The self-testing memory module of claim 5, wherein each of the plurality of data handlers is positioned closer to the corresponding plurality of data ports than to the other data ports of the plurality of memory devices.

\* \* \* \* \*

7. The self-testing memory module of claim 6, wherein each of the data handlers is further configured to read from the corresponding plurality of data ports and further comprises a verification element for checking for failures in the operation of the memory devices by verifying that data read from the corresponding plurality of data ports corresponds to the data generated by the data handler for writing to the corresponding plurality of data ports.

(JX-0003 at Cls. 1-3, 5-7.)

# B. Level of Ordinary Skill in the Art

The parties and Staff agree that a person of ordinary skill in the art would have "a Bachelor's degree in electrical engineering, computer engineering, or in a related field and at least one year of work experience relating to memory systems, and would be familiar with the design of memory devices, memory modules, and built-in-self test or BIST." (SIB at 30 (quoting

CPB at 87; RPB at 54).) The evidence of record further supports this definition of the level of ordinary skill in the art. (See CX-0005C at Q/A 96; CX-0931C at Q/A 101; RX-0008C at Q/A 30.) Accordingly, the undersigned finds that the level of ordinary skill in the art for the '434 patent is consistent with the definition proposed by the parties and Staff.

#### C. Claim Construction

There are four disputed claim terms relevant to the asserted claims of the '434 patent:

- 1. "self-testing memory module"

- 2. "generate"

- 3. "test"

- 4. "wherein the circuit is configured to test the memory devices"

Each is addressed in turn below.

# 1. "self-testing memory module"

The term "self-testing memory module" appears in independent claim 1, from which each of the asserted claims from the '434 patent depend. The parties propose the following constructions for this term:

| "self-testing memory module"                        |                                                                                                                    |                                                                                                                                                                                                                                 |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Complainant's Proposed Construction                 | Respondents' Proposed Construction                                                                                 | Staff's Proposed Construction                                                                                                                                                                                                   |  |

| No construction proposed  No construction necessary | memory module that is able to test one or more elements of the memory module without the use of an external device | plain and ordinary meaning, e.g., memory module that is able to test one or more elements of the memory module (either without the use of an external device or with the use of both an internal device and an external device) |  |

(SIB at 32; see also CIB at 23-24; RIB at 58.)

Complainant frames the dispute regarding this term as whether an external device can be used for any portion of the memory module self-test. (See CIB at 24.) Complainant's position is

that the term should not be construed to exclude the use of an external device during self-testing.

See id. In support of its position, Complainant points to the following portion of the specification:

<u>Some embodiments</u> described herein presents [sic] a self-testing memory module that can be <u>configured through an I2C interface</u> and that allows test results to be read out through the I2C interface. <u>Certain embodiments</u> described herein present a self-testing memory module that allows a test function to be configured, controlled, and/or executed <u>without substantial system memory controller involvement</u>. <u>Some embodiments</u> present a self-testing memory module that can be tested <u>without any external test equipment</u>.

(*Id.* (citing '434 patent at 3:46-54 (all emphases added)).) Complainant reads this passage to demonstrate that the '434 patent contemplates self-testing memory modules that interface with external devices. (*See id.* at 24-25.)

Complainant also points to a decision by the Patent Trial and Appeal Board ("PTAB" or "Board") of the U.S. Patent and Trademark Office, wherein the Board construed "self-testing memory module" to include memory modules that can be tested with a combination of internal and external test equipment. (*See id.* at 25 (citing IPR 2014-00970, Final Written Decision (Paper 32) at 14 (emphasis added)).) Complainant also relies on the testimony of its expert to support its construction. (*See* Mangione-Smith, Tr. at 426:2-20.)

By contrast, Respondents submit that this term should be construed to exclude the use of any external devices in the self-test. (See RIB at 58.) To support that position, Respondents point to the language of independent claim 1—the word "self" particularly—and argue that the claim language excludes the use of an external device. (See id.) Respondents also argue that independent claim 1 and unasserted independent claim 29 both describe testing procedures that "internally generate[] the requisite address and control signals and the requisite data for executing the test without an external device providing such signals." (Id.) Additionally, Respondents note that one of the stated purposes of the '434 patent is to obviate the expense associated with external testing of memory modules. (See JX-0003 at 1:58-2:5.)

Respondents also argue that an amendment made during the prosecution of the '434 patent supports construing "self-testing memory module" to exclude the use of an external device during testing. (See RIB at 58-59.) Specifically, Respondents submit that the examiner rejected the original claim 1 because it lacked any limitation related to self-testing. (See id.) That rejection was overcome by an amendment that added the limitation "wherein the circuit is configured to test the memory devices using the address and control signals generated by the control module and the data generated by the plurality of data handlers." (See id. at 59 (quoting JX-0009 at 151) (emphasis added).) Respondents interpret this portion of the prosecution history as a concession by the patentee "that 'self-testing' means testing using signals generated by circuits internal to the memory module and not signals provided by an external device." (Id.)

Finally, Respondents argue that Complainant is estopped from advancing its current claim construction argument because it argued for a narrower construction before the PTAB. (See id.)

Staff joins Complainant and argues that "self-testing memory module" should be construed according to its plain and ordinary meaning. Acknowledging that simply stating "plain and ordinary meaning" does not clearly resolve the dispute between the parties, Staff includes a parenthetical example with its proposed construction that explicitly states that the memory module may perform its self-test function "either without the use of an external device or with the use of both an internal device and an external device." (SIB at 32.) Staff argues that its construction is supported by the plain language of the claims, (*id.* at 33-36), and the specification, (*id.* at 36-40). Staff also argues that the prosecution history does not support construing "self-testing memory modules" to exclude any use of an external device. (*Id.* at 40-41.)

The undersigned agrees with the construction put forth by Complainant and Staff.

Contrary to Respondents' position, the claim term "self" does not provide a sufficient basis to

exclude the use of any external device during self-testing by a "self-testing memory module." This conclusion is particularly clear here, where the specification explicitly contemplates self-testing memory modules that make use of an external device. (See JX-0003 at 3:49-56.) Further, in its post-hearing reply brief, Respondents appear to concede that the proper construction of "self-testing memory module" should include configurations utilizing some external devices.<sup>4</sup> (RRB at 31 ("SK hynix's construction . . . allows some use of external equipment, such as configuring the memory module for testing and initiating the test but not actually executing the test . . . .").)

Accordingly, "self-testing memory modules" is construed to mean "memory module that is able to test one or more elements of the memory module (either without the use of an external device or with the use of both an internal device and an external device)."

#### 2. "generate"

The claim term "generate" appears in independent claim 1, from which each of the asserted claims from the '434 patent depend. The parties propose the following constructions for this term:

| "generate"                          |                                      |                                                                                                                                              |  |

|-------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Complainant's Proposed Construction | Respondents' Proposed Construction   | Staff's Proposed Construction                                                                                                                |  |

| produce or cause                    | produce (i.e., bring into existence) | produce (i.e., bring into existence, including by transformation or modification of information and/or data received from another component) |  |

Respondents submit that their construction allows use of external devices that perform "insubstantial" or "peripheral" functions related to testing. (See RRB at 31.) That interpretation is not supported by the actual language of Respondents' construction, nor was it raised in Respondents' initial brief. As such, the undersigned will not consider this belated modification to Respondents' proposed construction. Moreover, the undersigned notes that injecting the terms "insubstantial" and "peripheral" into the construction of "self-testing memory modules" would only add more uncertainty into the claim language.

(SIB at 43; see also CIB at 19-20; RIB at 49.)

Here, Complainant notes that all parties agree that "generate" should mean "produce," but that they disagree about whether that meaning includes transformation or modification of information and/or data received from another component. (See CIB at 20.) Complainant takes the position that transformation or modification of information and/or data received from another component is included within the proper construction of "generate." (See id.)

First, Complainant points to the language of independent claim 1, which ties the "generate" function to the data handlers within the claimed data module. (*See id.* at 20–21 (citing JX-0003 at 16:43-47).) Next, Complainant points to the specification for the proposition that data generated by the data handlers is created from information provided by the data module to the data handlers. (*See id.* at 21 (citing JX-0003 at 10:30-37).) Also, Complainant submits that "[t]he specification also explicitly contemplates the act of transforming or modifying incoming data as generating data within the meaning of the claim term . . . " (*Id.* (citing JX-0003 at 10:33-37).)

In addition to its reliance on the intrinsic evidence, Complainant also relies on expert testimony to support its construction. (*See id.*) Specifically, Complainant submits that Mr. Hoffman, one of Respondents' experts, testified that "generate" includes transformation of data. (*Id.* (citing Hoffman, Tr. 844:8-20)). Further, Complainant submits that its expert, Dr. Mangione-Smith, and Respondents' expert, Mr. Hoffman, agreed that Staff's proposed construction is consistent with the plain and ordinary meaning of "generate." (*See id.* at 21-22 (citing Mangione-Smith, Tr. at 427:2-18; Hoffman, Tr. at 834:9-18).)

Respondents also argue that Staff's proposed construction is correct. (See RIB at 49-50.) However, Respondents elaborate on that construction by arguing that Staff's construction includes data generated by the memory modules through transformation or modification of information

received from another source, but does not include "signals and data received by the data and control modules from another component, and merely provided, propagated, sent, input to memory devices, without transformation or modification the data and control modules." (*Id.* at 50 (quoting SPB at 49).) In short, Respondents' position is that while transformation or modification of external data is allowed, simple receipt of external data without any modification or transformation does not fall within the scope of the term "generate." (*See id.*) Respondents also take issue with the inclusion of the word "cause" in Complainant's proposed construction. (*See id.* at 50.)

Respondents argue that "the claims and specification distinguish between 'generate' and merely providing, writing, or inputting (*i.e.*, causing) data produced by a component other than the data handler." (*Id.* at 51 (citing RX-0348.028-32).) In support of that argument, Respondents point to the claims including both the words "generate" and "writing" as well as "generate" and "provide." (*Id.* (citing '434 patent at 16:42-48, JX-0004 at 16:42-46, JX-0005 at 18:16-20).) Respondents submit that the use of the words "writing" and "provide" in the same claim as "generate" means that "generate" cannot have the same meaning as those words. (*Id.* (citing *Z4 Tech., Inc. v. Microsoft Corp.*, 507 F.3d 1340, 1348 (Fed. Cir. 2007).)

Respondents also point to an example in the specification to support the proposition that "data generation involves an actual production of data." (*Id.*) Specifically, Respondents point to a passage stating that "data may be generated *based on previously written data* (e.g., *inverting each of the bits* of a previously written data word) in some embodiments." (*Id.* (citing JX-0003 at 10:57-60 (emphasis added by Respondents)).)

Respondents submit that construing "generate" to include "cause" would obviate one of the purposes of the patent—avoiding the use of expensive external memory testing equipment. (See id. at 52 (citing '434 patent at 1:58-2:5).) They also point to examples in the specification

where the memory module itself, as opposed to another testing device, actually produces the test data. (*Id.* (citing '434 patent at 3:28-41, Figs. 3, 5).)

Respondents argue that Complainant's own validity expert, Mr. Murphy, testified that simply using data provided without transforming it or modifying it would not meet the definition of "generate" to a person of ordinary skill in the art. (*Id.*) Somewhat confusingly though, Respondents support this assertion with a portion of their own expert's witness statement. (*See id.* (citing RX-1586C at Q/A 230, 232).)

A significant portion of Respondents' argument against construing "generate" to mean "cause" is based on the assertion that Complainant has taken a contradictory position before a district court in a parallel proceeding and before the PTAB in an Inter Partes Review ("IPR"). (See id. at 52-53.) With respect to the Complainant's position in the IPR, Respondents argue that Aylus Networks, Inc. v. Apple, Inc., 856 F.3d 1353 (Fed. Cir. 2017) establishes that statements made by a patentee during an IPR are part of the prosecution history for that patent, and thus can effect an estoppel. (See RIB at 53.) Because Complainant did not argue for a construction for "generate" that included "cause" during the IPR, but instead argued that "generate" should be construed to mean "produce (i.e., brought into existence)," Respondents submit that Complainant cannot argue for a construction of "generate" that encompasses "cause" in this Investigation. (See id.) Respondents go on to note that the PTAB construed "produce" to mean "originate," and not "merely providing, propagating, or sending the same information and/or data received from another component." (See id. (citing RX-0347 at 014).) Based on Complainant's statements during the IPR, Respondents argue that Complainant has disclaimed any construction of "generate" that includes "cause." (See id. at 53-54.)

Finally, Respondents submit that, prosecution disclaimer aside, Complainant has simply failed to provide any evidence supporting a construction of "generate" to mean "cause." (*See id.* at 54-55.)

Staff submits that the dispute between Complainant and Respondents over the construction of "generate" is one of form over substance. (SIB at 43.) Staff submits that despite providing different formulations of the construction for "generate," both parties have in fact agreed in substance with Staff's construction of "generate," which is based on PTAB's construction of "generate" in the IPR. (*Id.*) However, regardless of whether the parties agree with its construction, Staff submits that its construction is consistent with the intrinsic evidence, and thus should be adopted. (*Id.* at 45.)

First, Staff finds support for its construction in the language of the claims themselves. (See id. (citing JX-0003 at 16:42-48, 19:6-9).) Second, Staff points to Figure 3 of the specification, which discloses a "data generation element," to support its construction. (See id. at 45-46 (citing JX-0003 at Fig. 3, 10:27-37).) Third, Staff finds support for its construction in the IPR proceedings where the PTAB explained that its construction of "generate" would include the transformation or modification of information or data from another component, but would not include simple receipt of information or data by the data and control modules from another component without any kind of transformation or modification. (See id. at 46-47.)

With respect to extrinsic evidence, Staff points to the testimony of the parties' experts to further support its construction. Specifically, Staff submits that:

i) Respondents' expert, Mr. William Hoffman, testified that the Staff's proposed construction is consistent with the understanding of one of ordinary skill in the art of the '434 Patent who has reviewed the patent claims, specification, and prosecution history; and (ii) Complainant's expert, Dr. William Mangione-Smith, also testified that the Staff's proposed construction is consistent with the understanding of a person of ordinary skill in the art of the '434 Patent.

(*Id.* at 47 (citing Hoffman, Tr., 842:21-843:5; Mangione-Smith, Tr., 426:22-427:11).) Finally, addressing Respondents' prosecution disclaimer argument, Staff submits that the argument may provide an additional basis to reject a construction of "generate" that would encompass merely receiving or using data provided by another component. (*See id.* at 48.)

There appears to be a great amount of internal inconsistency in each party's arguments concerning the claim term "generate." Complainant, Respondents, and Staff all appear to agree that "generate" should be construed to mean: "produce (i.e., bring into existence, including by transformation or modification of information and/or data received from another component)." (See CRB at 2, n.1; RRB at 24-25; SRB at 10.) Yet, Complainant insists that Respondents and Staff seek a narrower construction that would limit the transformation or modification to a specific method: bit inversion. (See CRB at 3-4.) Respondents further insist that Complainant seeks a broad construction by the inclusion of the word "cause" in its proposed construction. (See RRB at 24-25.) In short, each party insists that they agree with Staff's proposed construction, while insisting that the other side does not. In such a situation, the undersigned will take each party at its own word, i.e., that a person of ordinary skill in the art would understand the plain and ordinary meaning of "generate" in the context of the '434 patent to mean "produce (i.e., bring into existence, including by transformation or modification of information and/or data received from another component)."

This construction is supported by the intrinsic evidence as well as extrinsic evidence in the form of expert testing at the evidentiary hearing. Specifically, "generate" appears in independent claim 1 of the '434 patent as follows:

a control module configured to *generate* address and control signals for testing the memory devices; and a data module comprising a plurality of data handlers, each data handler operable independently from each of the other data handlers of the plurality of data handlers and operatively coupled to a corresponding plurality of the

data ports of one or more of the memory devices and configured to *generate* data for writing to the corresponding plurality of data ports, wherein the circuit is configured to test the memory devices using the address and control signals *generated* by the control module and the data *generated* by the plurality of data handlers.

(JX-0003 at Cl. 1 (emphasis added).) Construing "generate" to mean "produce" or "bring into existence" is consistent with the manner in which "generate" is used in this claim. Construing "generate" to mean "cause," however, is not. Construing "generate" to mean "cause" would produce nonsensical results, such as "a control module configured to [cause] address and control signals," and a "plurality of data handlers . . . configured to [cause] data for writing to the corresponding plurality of data ports." (*Cf. id.* (alterations substituting "cause" for "generate").) Moreover, no part of the claim language suggests that production by transformation or modification should be excluded from the definition of "generate."

Further, Figure 3 of the '434 patent discloses a data generation element numbered 54 in the figure. The specification provides the following discussion of that element:

Each of the data handlers 30 of certain embodiments further includes a data handler logic element 46. The data handler logic element 46 of certain embodiments comprises a data generation element 54 and a verification element 56. The data generation element 54 may be configured to generate data signals (e.g., patterns of data signals) for writing to the corresponding plurality of data ports, for example. The data signals and/or patterns of data signals may be based on information (e.g., programming or configuration information) the data handler logic element 46 receives from the control module 22, for example.

\* \* \*

The data may be generated in a variety of ways. In one embodiment, the data is generated based on a current write address value. For example, in one example configuration, on a first write cycle, hexadecimal "A's" are generated and written to even address locations and hexadecimal "S's" are generated and written to odd address locations, and on a second write cycle, "S's" are written to even addresses and "A's" are written to odd addresses, and this pattern repeats in subsequent cycles. The data may be generated based previously written data (e.g., inverting each of the bits of a previously written data word) in 60 some embodiments. In general, any manner of generating a cyclic or otherwise deterministic data pattern may be compatible with embodiments described herein. In other embodiments, random or pseudorandom data may be generated and written to the corresponding

plurality of data ports. For 65 example, a linear feedback shift register (LFSR) may be used in some embodiments.